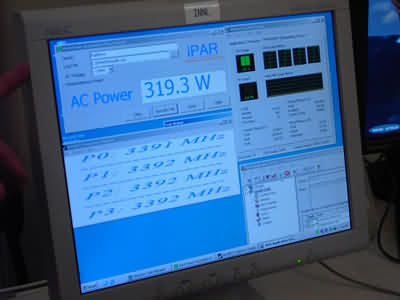

В рамках российского форума IDF-2004 на докладе Ричарда Вирта, а также на отдельном стенде, именуемом «Intel Xeon processor with Intel Extended Memory 64 Technology» корпорация Intel представила новую технологию управления режимами производительности и энергопотребления серверной линейки процессоров Intel Xeon с поддержкой технологии EM64T, основанных на ядре Nocona, продемонстрировав ее в действии на двухпроцессорной системе с процессорами Intel Xeon 3.4 ГГц с технологией Hyper-Threading. Измерение частоты процессоров проводилось с помощью фирменной утилиты Intel Frequency Display, а измерение общей потребляемой системой мощности – с помощью внешнего датчика, расположенного непосредственно в цепи питания. В качестве нагрузки для процессоров использовался стресс-тест, имитирующий реальную нагрузку на веб-сервер, при этом частота обеих процессоров изменялась в интервале от 2.8 ГГц при минимальной нагрузке до 3.4 ГГц при максимальной. Вот что рассказал присутствовавший при тестировании Дмитрий Беседин, автор тестовых пакетов комплекта RightMark:

"Технология, получившая кодовое название DBS (Demand Based Switching), а официальное – Intel SpeedStep (весьма привычное для пользователей мобильных ПК с технологией Intel Centrino), позволяет изменять коэффициент умножения и питающее напряжение процессора в зависимости от степени его загрузки. Какие-либо технические детали реализации технологии (измерения загрузки процессора и его частоты, а также скорости переключения состояний) не разглашались, однако, нашими специалистами была обнаружена весьма интересная деталь, связанная с изменением частоты процессора. При минимальной его частоте, равной 2.8 ГГц согласно Intel Frequency Display, его фактическая частота, измеренная с помощью как нашей утилиты RMSpy, так и CPU-Z, по-прежнему оказывалась равной... 3.4 ГГц. По крайней мере, можно с уверенностью констатировать нижеследующее: переключение режимов работы процессора не приводит к изменению его внутреннего тактирования, отображаемого счетчиком тактов (TSC), на основе которого и измеряется реальная частота процессора в утилитах вроде RMSpy и CPU-Z. При этом утилита CPU-Z выявила дополнительную подробность – коэффициент умножения процессора, считываемый из модель-специфичных регистров (MSR), действительно изменяется в интервале от 14 до 17 (при изменении его «частоты» от 2.8 до 3.4 ГГц, соответственно), что сопровождается артефактным изменением частоты FSB (от 242.8 до 200.0 МГц, соответственно), поскольку в основе ее вычисления лежит простое деление измеренной частоты процессора на его коэффициент умножения. Надо признаться, что столь интересная особенность поведения новой разновидности технологии Intel SpeedStep весьма удивила даже сотрудников Intel, ответственных за проведение демонстрации."