Часть 3: организация кэшей данных, внешние интерфейсы процессора, эволюция и ближайшие перспективы развития

Часть 1: общая организация, кэш инструкций и предсказание переходов, выборка и декодирование

Часть 2: внеочередное исполнение операций и функциональные устройства

Организация кэшей данных, внешние интерфейсы процессора

Устройство кэшей 1-го и 2-го уровня

Все рассматриваемые процессоры имеют отдельные кэши 1-го уровня (L1-кэши) для инструкций и данных, и общий кэш 2-го уровня (L2-кэш) увеличенного размера. Кэши инструкций различаются по своей организации: в процессорах Intel P-III, P-M, P-M2, P8 и IBM PPC970 в них хранятся исходные машинные инструкции в неизменённом виде. В процессорах AMD K8 — исходные инструкции вместе с информацией об их разметке (предекодировании), а в процессоре Intel P-4 — полностью декодированные микрооперации (МОПы), организованные в виде трасс. Общее описание устройства кэшей инструкций было дано выше, в соответствующем разделе.

Организация кэшей данных 1-го уровня в целом соответствует организации классического кэша инструкций. Например, в процессорах P-M, P-M2 и P8 общая структура кэшей инструкций и данных полностью совпадает: размер составляет 32 Кбайт, уровень ассоциативности — 8, размер блока — 64 байта. Также совпадает структура кэшей в процессоре K8: размер — 64 Кбайт, ассоциативность — 2, блок — 64 байта. Как видим, в процессоре K8 кэши имеют вдвое больший размер, но весьма малый уровень ассоциативности, а связи с чем могут возникать конфликты по алиасингу и снижаться их эффективная вместимость.

В процессоре PPC970 между кэшами есть различия: кэш инструкций имеет размер 64 Кбайт и ассоциативность 1, а кэш данных — размер 32 Кбайт и ассоциативность 2. Размер блока для обоих кэшей равен 128. Организация кэшей с увеличенным размером блока и очень низкой ассоциативностью существенно снижает их эффективный размер и ведёт к значительным потерям на фрагментацию.

Для всех указанных процессоров время доступа к кэшу данных 1-го уровня составляет 3 такта.

В процессоре P-4 кэш данных по своей организации несколько отличается от кэшей других процессоров. Он имеет небольшой размер (8 Кбайт при уровне ассоциативности 4) и очень низкое время доступа — всего 2 такта (это соответствует примерно 1.5 тактам в традиционных процессорах). Столь быстрый доступ к кэшу обеспечивается применением ряда приёмов: тесной интеграцией кэша с арифметико-логическим и адресным устройствами, удвоенной частотой работы этих устройств и использованием 16 младших разрядов программного (логического) адреса для спекулятивной выборки элемента данных. Для адресации требуемого набора в кэше используются соответствующие разряды адреса b10-5, а для «предварительного» нахождения блока в этом наборе — всего 5 следующих разрядов b15-11 (эти разряды называют мини-тэгом). Окончательная проверка старших разрядов адреса (ключа) на соответствие полному тэгу вместе с преобразованием программного адреса в физический производится позднее. Если при этой проверке выяснится, что данные были считаны неправильно, они помечаются как недействительные, и производится их считывание из L2-кэша (как и в случае ненахождения данных в L1-кэше).

Использование мини-тэга для спекулятивного считывания данных порождает острую проблему алиасинга: в одном наборе кэша не может быть двух блоков данных с совпадающими мини-тэгами, то есть отстоящих друг от друга на расстоянии, кратном 64 Кбайт. Это делает такой кэш похожим на кэш с прямым отображением (то есть с ассоциативностью, равной 1). Кроме того, конфликт по мини-тэгу усложняет процедуру считывания корректных данных из L2-кэша и может значительно увеличить время этого считывания. Данная аномалия может приводить к чрезмерной работе системы реплея и к снижению производительности.

В процессоре P-4E (Prescott) организация кэша данных изменилась. Его размер увеличился до 16 Кбайт, уровень ассоциативности — до 8, а время доступа выросло до 4 тактов (что соответствует примерно 3 тактам в традиционных процессорах). Изменение времени доступа связано с увеличением размера и уровня ассоциативности и с повышением разрядности мини-тэга, а также с удлинением на 0.5 такта этапа подготовки адреса. Размер мини-тэга был увеличен с 5 до 10 разрядов (b20-11), а кратность адресов по мини-тэгу — до 2 Мбайт, благодаря чему проблема алиасинга практически исчезла. В связи с этим резко снизились потери на неправильное считывание данных из L1-кэша, что частично компенсировало возросшее время доступа.

Кэши 2-го уровня в рассматриваемых процессорах имеют примерно одинаковую общую организацию. Размер блока L2-кэша в современных процессорах составляет 64 или 128 байт. Кэш 2-го уровня соединён с L1-кэшами полночастотной шиной, ширина которой может достигать 32 байта (256 бит), а пропускная способность — 121.6 Гбайт/с (для процессора P-4E 3.8 ГГц). В процессоре K8 шина L2-кэша имеет ширину 16 байтов (128 бит) и пропускную способность 48 Гбайт/с (при частоте процессора 3.0 ГГц). Однако из-за необходимости копировать в L2-кэш данные, вытесняемые из L1-кэша (в связи с взаимно эксклюзивной организацией кэшей в этом процессоре), эффективный темп считывания из L2-кэша снижается вдвое. В двухъядерных процессорах P-M2 (Core Duo) и P8 (Core) используется L2-кэш, общий для обоих ядер.

Размеры L2-кэшей очень сильно варьируются в пределах каждого семейства процессоров. Приведём максимальные размеры и значения уровней ассоциативности для различных семейств: P-III — 512K (8), P-M — 2M (8), P-M2 — 2M (8), P-4 — 512K (8), P-4E — 2M (8), P8 — 4M (16), K8 — 1M (16), PPC970 — 512K (8), PPC970MP — 1M.

Время доступа к L2-кэшу не является однозначной величиной и в ряде случаев может зависеть от нагрузки (частоты обращений). В документации по процессорам обычно приводят «чистые» значения, которые бывает трудно воспроизвести в тестах. Можно дать следующие примерные оценки полного времени доступа к данным в L2-кэше в тактах (по результатам тестирования на сайте iXBT.com): P-III — 8, P-M — 10, P-4 — 19 (9), P-4E — 29 (22), P-M2 — 14, P8 — 14, K8 — 17 (12). Для процессоров P-4, P-4E и K8 в скобках показаны «минимальные» значения времени доступа, полученные с помощью специальных приёмов тестирования, когда производилась «разгрузка» шины L2-кэша. Отметим, что в процессорах P-4 и P-4E длина такта меньше, чем в других процессорах, и время доступа к их кэшам (без «разгрузки» шины), выраженное в «нормализованных» тактах с учётом соотношения 1:1.4, составит соответственно 14 и 21 такт.

Механизмы вытеснения блоков из кэшей

Рассмотрим теперь механизмы вытеснения блоков данных из кэшей в случаях, когда необходимо освободить место для новых блоков. Существует несколько способов организации кэшей в этой части. Основным отличительным признаком является момент времени, когда в кэш следующего уровня переписывается вытесняемый модифицированный блок данных — то есть такой блок, в который с момента загрузки его в кэш произошла запись (и содержимое которого изменилось). Запись модифицированных данных в кэш более высокого уровня (L2-кэш) может происходить либо одновременно с их записью в L1-кэш, либо позднее, в момент вытеснения блока из L1-кэша. При вытеснении не модифицированного блока он обычно просто удаляется, однако при так называемой «эксклюзивной» организации он также переписывается в L2-кэш.

На практике встречаются следующие разновидности кэшей:

- Write-through — со сквозной (немедленной) записью модифицированных данных в L2-кэш;

- Write-back — с отложенной записью модифицированных данных из L1-кэша в L2-кэш;

- Exclusive — эксклюзивный, с отложенной записью из L1-кэша в L2-кэш как модифицированных, так и не модифицированных (чистых) данных.

В процессорах P-4 и PPC970 используется L1-кэш со сквозной записью, в P-III, P-M, P-M2 и P8 — L1-кэш с отложенной записью, а в K8 — эксклюзивный кэш.

Каждый из двух основных механизмов (со сквозной и с отложенной записью) имеет свои преимущества и недостатки. Сквозная запись увеличивает нагрузку на L2-кэш, так как при каждой записи данных в L1-кэш производится их немедленное копирование в L2. С другой стороны, при необходимости освободить место в L1-кэше такой модифицированный блок может быть немедленно удалён из него, так как в L2-кэше уже имеется его копия. При отложенной записи копирование в L2-кэш производится только в момент вытеснения модифицированного блока — что позволяет избегать лишних пересылок данных, но приводит к усложнению кэшей и необходимости создания очереди для буферизации вытесняемых блоков.

Термин «эксклюзивный» обычно относят к кэшу 2-го уровня, но на самом деле это совместное свойство обоих кэшей — L1 и L2. При такой организации искусственно поддерживается состояние, когда блок данных хранится только в одном из кэшей — L1 либо L2. При первоначальной загрузке из памяти блок помещается непосредственно в L1-кэш, минуя L2-кэш. При вытеснении из L1-кэша этот блок переписывается в L2-кэш для последующего сохранения (даже если он не был модифицирован). При повторном считывании блока из L2-кэша в L1-кэш он снова удаляется из L2-кэша.

Необходимость копирования не модифицированных данных при вытеснении блока приводит к дополнительной нагрузке на шины передачи данных и может увеличить эффективное время доступа к L2-кэшу. С другой стороны, эффективный размер L2-кэша при эксклюзивной организации увеличивается. Например, в случае тяжёлой нагрузки на кэши данных этот эффективный размер может достигать суммы размеров кэшей L1 и L2, что подтверждается тестами.

В процессоре K8 кэш инструкций также имеет эксклюзивную организацию. Такая организация позволяет при вытеснении блоков с инструкциями сохранять в L2-кэше также и служебную информацию об истории условных переходов — так называемые селекторы переходов (branch selectors). Они записываются в поля ECC (кода контроля ошибок) L2-кэша и восстанавливаются при повторном считывании инструкций в L1-кэш. Эксклюзивная организация кэша инструкций приводит к дополнительному увеличению эффективного размера L2-кэша.

«Не-эксклюзивная» организация кэшей L1 и L2 не подразумевает их обязательной «инклюзивности» — блок данных или инструкций может быть вытеснен из L2-кэша и при этом сохраниться в соответствующем L1-кэше. Таким не-эксклюзивным (но и не инклюзивным) способом организованы кэши в процессорах P-III, P-4, P-M, P-M2 и P8.

В процессоре PPC970 L1-кэш организован чисто инклюзивно по отношении к L2-кэшу. При вытеснении блока из L2-кэша проверяется, не сохранился ли он в L1-кэше — и в этом случае искусственно удаляется оттуда тоже. Наряду с использованием механизма сквозной записи для вытеснения данных из L1-кэша это позволяет упростить так называемую проверку когерентности кэшей в многопроцессорной (многоядерной) системе, когда другой CPU проверяет наличие данных в кэшах текущего CPU. При инклюзивной организации достаточно ограничиться проверкой L2-кэша, в то время как при других организациях необходимо проверять кэши обоих уровней.

Вытеснение модифицированных данных из кэша 2-го уровня в память всегда производится по механизму отложенной записи.

Вопросы повышения эффективности доступа к данным

В современных процессорах имеются различные средства, позволяющие повысить эффективность доступа к данным в памяти и снизить потери на ожидание их прихода, а также прочие задержки и затраты на организацию этого доступа. Наиболее важными из этих средств являются механизмы предвыборки из памяти. В каждом из рассматриваемых процессоров реализовано два таких механизма — программная предвыборка (software prefetch), и автоматическая аппаратная предвыборка (hardware prefetch).

Наличие машинных инструкций программной предвыборки позволяет организовать пересылку данных из оперативной памяти в кэши процессора заблаговременно, с таких расчётом, чтобы ко времени использования этих данных они уже оказались бы в кэшах. Особенность операции предвыборки состоит в том, что она лишь инициирует считывание данных из памяти, после чего считается завершённой. В отличие от обычной операции доступа к памяти, операция предвыборки не должна ожидать прихода данных в конкретный регистр, поэтому она не блокирует другие операции в буфере переупорядочения ROB и может быть отправлена в отставку немедленно. Использование же операции фиктивной загрузки данных в регистр (с целью ускорения их прихода в кэш) привело бы к такому блокированию — несмотря на то, что значение, считанное в регистр, не понадобилось бы никакой другой операции.

Существуют различные варианты инструкций предвыборки — считывание из памяти в L2-кэш, считывание из памяти или из L2-кэша в L1-кэш, считывание блока для его последующей модификации, либо для одноразового использования. В процессоре P-4 реализована предвыборка только в L2-кэш.

Автоматическая аппаратная предвыборка представляет собой механизм, который распознаёт последовательные (или иные регулярные) обращения в память и пытается производить опережающую подкачку данных. В некоторых процессорах этот механизм умеет работать как в прямом, так и в обратном направлении (то есть как по возрастанию, так и по убыванию адресов в памяти) и может распознавать несколько независимых последовательностей адресов, обеспечивая тем самым предвыборку нескольких потоков данных.

Наиболее совершенные механизмы программной и аппаратной предвыборки реализованы в новом процессоре P8 (Intel Core).

Ещё один механизм работы с памятью связан с особенностями загрузки и выгрузки в условиях внеочередного исполнения. В связи с тем, что операция может считаться корректно выполненной только к моменту ухода в отставку и не ранее, чем будет отставлены все предшествующие операции, физическая запись в кэши или в память не может быть произведена до этого момента. По этой причине все результаты выгрузки (записи) в память накапливаются в специальном буфере упорядочения обращений к памяти MOB (Memory Order Buffer). Физическая запись данных из этого буфера в кэш производится только в момент отставки соответствующей инструкции. Если операция загрузки (чтения) из памяти адресует элемент данных, который оказался в этом буфере, то он считывается непосредственно из буфера.

В условиях внеочередного исполнения может получиться, что операция загрузки окажется готовой к выполнению раньше, чем выполнится операция выгрузки, записывающая данные в память по тому же адресу. Также может оказаться, что адрес данных в какой-либо операции выгрузки ещё не вычислен, и есть риск, что рассматриваемая операция загрузки могла бы обратиться как раз к этим данным по этому адресу. Чтобы избежать проблем такого рода, в процессорах обычно реализуют консервативные схемы управления операциями обращения в память, с запретом на выполнение любых рискованных операций, которые могли бы привести к чтению некорректных данных. Однако такие консервативные схемы могут помешать внеочередному исполнению «безопасных» операций и привести к снижению производительности.

На практике вероятность конфликтов по адресам такого рода обычно невелика. Поэтому при наличии в процессоре механизма восстановления в случае выполнения некорректной операции обращения в память можно было бы отказаться от запрета на выполнение рискованных операций. В процессоре P8 (Intel Core) такой механизм реализован — он идентичен механизму восстановления после неправильно предсказанного перехода, когда в момент отставки инструкции перехода производится окончательная проверка правильности предсказания.

Помимо механизма восстановления, в процессоре P8 имеется также дополнительный «предсказатель», назначение которого состоит в снижении вероятности исполнения рискованной операции загрузки из памяти. Если такой загрузке предшествует операция выгрузки с не вычисленным (на данный момент) адресом памяти, производится предсказание конфликта по адресам на основе информации о предыдущем поведении этой операции загрузки. Если предсказывается отсутствие конфликта, операция загрузки запускается на выполнение. Если в момент отставки этой инструкции выяснится, что предсказание было неверным, и произошёл конфликт по адресам с операцией выгрузки, то операция загрузки будет отменена вместе со всеми последующими операциями, и будет произведено её повторное выполнение. Описанный механизм получил название «устранение неоднозначностей в памяти» (Memory Disambiguation).

В заключение рассмотрим ещё один микроархитектурный механизм, который связан с вычислением адресов для обращений в память — работу с аппаратным стеком. Адрес вершины аппаратного стека хранится в регистре ESP. Изменение этого регистра может происходить как неявно, при помещении или удалении данных из стека (инструкции PUSH и POP) либо при входе или выходе в подпрограмму (инструкции CALL и RET), так и явно, в обычной целочисленной инструкции. Традиционно инструкции, использующие регистр ESP и неявно изменяющие его, преобразовывались декодером в два МОПа, один из которых производил содержательное действие, а другой — выполнял операцию сложения или вычитания для регистра ESP.

В процессорах P-M, P-M2 и P8 введён специальный механизм под названием «Dedicated Stack Engine». Этот механизм отслеживает (на этапе декодирования инструкций) текущее положение вершины стека и заменяет в порождаемых МОПах адресацию данных по «меняющемуся» регистру ESP на сумму некоторого «постоянного» базового адреса стека и отслеживаемого смещения. Таким образом, отпадает необходимость постоянно модифицировать регистр ESP — теперь его нужно вычислять только в случае явного использования в качестве операнда или индекса. Благодаря этому исчезают ненужные зависимости между операциями по этому регистру, снижается число МОПов в указанных инструкциях (с двух до одного), повышается эффективность работы декодера и увеличивается общая производительность процессора.

Внешние интерфейсы процессоров

Рассмотрим кратко организацию внешних интерфейсов процессоров, через которые они обращаются к оперативной памяти и внешним устройствам, а также с другим процессором в составе многопроцессорной (многоядерной) системы.

Наиболее традиционным способом организации внешнего интерфейса является шина FSB (Front Side Bus), используемая в процессорах компании Intel. В процессорах P-M, P-M2, P-4 и P8 используется одинаковая (по организации и протоколу) 64-битная шина с «учетверённой» скоростью передачи данных QDR (Quad Data Rate). Шина FSB соединяет один или два процессора (иногда больше) и контроллер, обеспечивающий доступ к оперативной памяти и внешним устройствам. Этот контроллер входит в состав набора системной логики (чипсета), его обычно называют «Northbridge» («Северный мост»).

В каждом такте синхронизации шины по ней может быть передана команда либо четыре порции данных по 64 бита (8 байт). Частота синхронизации шины находится в диапазоне 200-266 МГц для процессоров P-4/P-4E, и 266-333 МГц для процессоров P8. Это соответствует частоте передачи 8-байтных порций данных, равной 800-1066 МГц и 1066-1333 МГц, и предельной скорости передачи данных из памяти (в память) 6.4-8.5 Гбайт/с и 8.5-10.6 Гбайт/с.

Шинная организация системы имеет свои недостатки. В системе, содержащей два или более процессоров (процессорных ядер), шина FSB ограничивает пропускную способность при доступе в память. Использование режима передачи данных QDR с относительно невысокой частотой синхронизации приводит к дополнительным потерям времени при обращении в память — на обращение тратится несколько тактов синхронизации шины, что может увеличить латентность доступа на 20-25 нс и более. Наконец, шина FSB может являться узким местом при наличии внешних устройств с очень высоким темпом передачи данных (например, коммуникационных контроллеров в кластерах). Для ослабления ограничений такого рода иногда используют многошинную организацию систем, когда, например, две пары процессоров группируются на двух независимых шинах, которые объединяются (управляются) специальным контроллером.

Несколько иначе организован внешний интерфейс в процессоре IBM PPC970. Он соединяется с контроллером памяти через два однонаправленных 32-битных канала (последовательные шины) — один для чтения из памяти, другой для записи. Данные передаются с «удвоенной» скоростью (DDR, Double Data Rate). Предельная скорость передачи данных по каждому каналу может достигать 5 Гбайт/с (для процессора с частотой 2.5 ГГц), однако в силу последовательной организации реально достигается скорость на уровне 90% от предельной. Достаточно высокая частота синхронизации позволяет несколько снизить потери времени на доступ, однако скорость канала недостаточна для чтения данных из памяти в необходимом темпе.

Наиболее интересным образом организованы интерфейсы в процессоре AMD K8. На кристалле этого процессора содержится встроенный контроллер оперативной памяти, непосредственно управляющий сигналами, посылаемыми на микросхемы памяти. Поскольку управляющая логика такого контроллера непосредственно связана с ядром процессора и может работать на высокой частоте, исключаются потери времени на доступ к данным. В сравнении с процессорами на шине FSB, время доступа к памяти может оказаться примерно в полтора раза ниже (например, 45-50 нс против 70 нс), что повышает производительность процессора за счёт снижения потерь на ожидание данных. Современные варианты процессоров K8 могут работать с двумя каналами памяти DDR-400, обеспечивая предельную пропускную способность в 6.4 Гбайт/с. В настоящее время осуществляется переход к поддержке памяти DDR2-667 и DDR2-800, что позволит повысить пиковую пропускную способность до 10.6 Гбайт/с и 12.8 Гбайт/с, соответственно.

Взаимодействие с контроллером внешних устройств осуществляется через специальные высокоскоростные последовательные каналы HyperTransport (HT). Всего в процессоре может быть три таких канала с частотой синхронизации 1 ГГц при «удвоенной» скорости передачи (DDR). Каждый канал состоит из двух однонаправленных шин шириной 16 бит (2 байта). Предельная скорость передачи данных составляет 4 Гбайт/с (в каждом направлении), реальная — несколько ниже.

Три канала HT могут быть использованы для объединения двух и более процессоров в многопроцессорную систему с общей памятью. В этой системе каждый процессор имеет собственную, индивидуальную оперативную память, доступ к которой может осуществляться из любого процессора. Выбор нужного канала HT, и последующая маршрутизация запроса производится автоматически, на аппаратном уровне. По существу, при доступе в «чужую» (нелокальную) память канал HT исполняет роль системной шины, а удалённый процессор — роль контроллера памяти. Латентность при доступе к «чужой» памяти выше, чем к локальной, а темп чтения — существенно ниже. Поэтому число процессоров в многопроцессорной системе обычно не превышает двух или четырёх (при максимуме восемь), а высокая эффективность вычислений достигается лишь при исполнении достаточно независимых программ, «привязанных» к конкретному процессору и его локальной памяти.

Реализация контроллера памяти, встроенного в процессор, имеет много преимуществ для использования в десктопных компьютерах. Она способствует ощутимому повышению производительности и упрощению структуры системы. Также очень выгодным является использование таких процессоров в кластерах, построенных на двух- и четырёхпроцессорных вычислительных узлах — наличие индивидуального контроллера памяти в каждом процессоре позволяет обеспечить высокий темп чтения из памяти и, как следствие, высокий уровень производительности.

Однако встроенный контроллер памяти имеет и свои недостатки. В связи с тем, что повышаются электрические требования к процессору с встроенным контроллером, бывает затруднено использование конфигураций с большим количеством чипов памяти, либо в таких конфигурациях происходит снижение скоростных характеристик памяти. В ряде случаев приходится прибегать к применению так называемой буферизованной (регистровой) памяти, которая создаёт меньшую электрическую нагрузку, но при этом имеет худшие скоростные характеристики. При создании систем с общей памятью возникают проблемы с организацией вычислений, поскольку такие системы являются неоднородными по доступу к памяти — время и скорость доступа к локальной и «чужой» памяти сильно различаются.

По всей видимости, с повышением скорости работы памяти и увеличением потребностей процессоров в пропускной способности от использования встроенных контроллеров придётся отказаться — они будут заменены вынесенными индивидуальными контроллерами, соединяемыми с процессорами при помощи высокоскоростных шин.

Эволюция и ближайшие перспективы развития процессорных микроархитектур

Итак, мы завершили рассмотрение основных подсистем современных десктопных процессоров. В заключение подведём краткие итоги развития процессорных микроархитектур в последние годы и рассмотрим их ближайшие перспективы. Рассмотрение будем вести по компаниям-производителям.

Процессоры компании Intel

Развитие современных процессорных микроархитектур у компании Intel шло по извилистому пути. После появления в 1995 г. процессора Pentium Pro, первого представителя архитектуры P6, происходило плавное усовершенствование, завершившееся выходом процессора Pentium III (1999 г.). Одновременно с этим разрабатывалась новая, революционная микроархитектура NetBurst (P7), первый представитель которой (Pentium 4) появился в 2000 г. Дальнейшим развитием этого семейства явился процессор Prescott (P-4E, 2004 г.), имеющий определённые микроархитектурные отличия от первоначального процессора P-4 и поддерживающий 64-битный режим целочисленной и адресной арифметики EM64T (x86-64).

Процессор P-4 был ориентирован на достижение высокой производительности в первую очередь за счёт повышения тактовой частоты (в 1.4-1.5 раза по сравнению с классическими процессорами, исполненными по той же электронной технологии) в сочетании с применением ряда принципиальных новшеств в микроархитектуре. Всё это привело к значительному увеличению длины конвейера и к усложнению различных подсистем процессора — и, как следствие, к возрастанию энергопотребления и тепловыделения. В результате с ростом тактовой частоты суммарное тепловыделение приблизилось к предельно допустимым значениям (для десктопных применений). Особо наглядно это проявилось при создании и внедрении двухъядерных процессоров. Другой причиной, снижающей интерес потребителей к процессорам данного семейства, являлось повышенное требование длинноконвейерной архитектуры NetBurst к оптимизации матобеспечения, что не нашло адекватного отклика у создателей программных средств.

В связи с возникшими проблемами компания Intel вернулась к эволюционному развитию старого доброго семейства P6. Первоначально это развитие происходило параллельно с развитием архитектуры NetBurst и выразилось в появлении процессора Pentium M (2003 г.), ориентированного на применение в мобильных компьютерах. В связи с этой ориентацией, основной упор был направлен на снижение энергопотребления подсистемами процессора, а также на введение различных экономичных режимов работы. Одновременно производилось устранение основных недостатков процессора P-III и внедрение некоторых принципиальных микроархитектурных расширений.

Процессор Pentium M оказался довольно успешным и демонстрировал достаточно высокую производительность в некоторых применениях, подтверждая удачность основных принципов, на которых была построена микроархитектура семейства P6/P6+. Поэтому не удивительно, что разработчики приняли решение создать новую микроархитектуру, базирующуюся на тех же принципах и значительно расширяющую её. В новой архитектуре Intel Core (P8, 2006 г.) устранено большинство недостатков предшественников, увеличена «ширина обработки», существенно ускорен блок арифметики с плавающей точкой и добавлена поддержка 64-битного режима EM64T (x86-64). В результате получился добротный «классический» процессор с широкой динамической архитектурой. Несмотря на более низкую тактовую частоту, он заметно превосходит процессоры семейства NetBurst по производительности в подавляющем большинстве применений — в первую очередь за счёт увеличения числа операций, выполняемых в каждом такте, а также за счёт снижения потерь, обусловленных большой длиной конвейера.

Проведём краткое сопоставление процессоров P-4 и P8 со своим общим предшественником P-III.

Микроархитектура процессора P-4 содержит два класса отличий от P-III — «революционные» и «эволюционные». К числу революционных можно отнести нововведения, которые обусловлены необходимостью увеличения тактовой частоты и снижения длины такта:

- кэш трасс (Т-кэш) для хранения декодированных микроопераций (МОПов), используемый вместо классического кэша инструкций;

- механизм ранней спекулятивной диспетчеризации (запуска на исполнения) МОПов с их перезапуском (в случае необходимости) после ожидания в «петле реплея»;

- работа быстрого арифметико-логического устройства на удвоенной частоте при тесной интеграции с L1-кэшем вкупе со спекулятивной выборкой данных из L1-кэша.

Эти революционные изменения отличают архитектуру NetBurst от процессоров «классической» архитектуры. Одновременно с этим, процессор P-4 содержит также ряд эволюционных нововведений и усовершенствований:

- значительное изменение структуры системы внеочередного исполнения, увеличение длины буферов и очередей, изменение организации функциональных устройств;

- радикальное улучшение подсистемы предсказания переходов;

- обработка 128-битных регистров SSE в одной операции с расщеплением на 64-битные подоперации в функциональном устройстве (правда, за счёт снижения темпа обработки вдвое);

- введение режима EM64T (x86-64) в процессоре P-4E;

- множество отличий в различных подсистемах (переименование регистров, трансляция логических адресов в физические, предвыборка данных и проч.);

- новая, более производительная внешняя шина FSB.

Большинство недостатков процессора P-4 являются следствием нововведений, направленных на достижение высокой производительности — повышенной тактовой частоты и увеличенной длины конвейера, а также спекулятивного характера многих действий и оптимизации выполнения «типичных» операций в ущерб «нетипичным». Основными недостатками являются:

- острая проблема алиасинга при выборке данных из L1-кэша и, как следствие, значительные потери на реплей (в первоначальном процессоре P-4);

- половинная частота запуска скалярных операций SSE;

- неэффективная реализация некоторых операций сдвига (всех сдвигов в процессоре P-4, сдвигов вправо и циклических в 64-битном режиме в процессоре P-4E);

- высокая латентность инструкций, работающих с флагом переноса CF (ADC, SBB);

- большая длина конвейера непредсказанного перехода;

- недостаточная эффективность Т-кэша для плохо структурированных кодов;

- малый размер L1-кэша и высокая латентность доступа к L2-кэшу.

В целом, процессоры P-4/P-4E были довольно успешными и получили массовое распространение, но срок жизни семейства оказался не столь продолжительным, как ожидалось изначально — несмотря на то, что архитектура NetBurst обогнала своё время. Причины и уроки развития этой архитектуры ещё предстоит осмыслить.

Основные отличия двухъядерного процессора P8 от своего идеологического предшественника P-III также можно разделить на две группы. К первой следует отнести различные усовершенствования и исправления недостатков, проведённые поэтапно в процессорах семейства P6+ (P-M и P-M2):

- увеличены размеры и ассоциативность кэшей;

- увеличены размеры очередей внеочередного исполнения и различных внутренних таблиц;

- радикально улучшена подсистема предсказания переходов;

- введён механизм слияния микроопераций (micro-op fusion);

- ускорена работа с аппаратным стеком;

- значительно усовершенствован декодер машинных инструкций;

- добавлены режимы SSE2 и SSE3, проведён ряд усовершенствований в функциональных устройствах и портах запуска операций;

- заимствована внешняя шина FSB у процессора P-4;

- внедрены усовершенствованные технологии энергосбережения;

- реализована двухъядерность с общим L2-кэшем (в процессоре P-M2).

Во вторую группу входят нововведения, появившиеся в архитектуре P8 и отличающие её от промежуточной архитектуры P6+:

- увеличена «ширина обработки» до 4-5 инструкций за такт, введён механизм слияния в одну макрооперацию инструкций сравнения и перехода;

- увеличено число кластеров арифметико-логических функциональных устройств и портов запуска;

- увеличены размеры очередей внеочередного исполнения и различных таблиц;

- усовершенствованы подсистемы предсказания переходов и предвыборки данных;

- добавлен механизм устранения неоднозначностей при обращении в память;

- реализован полночастотный 128-битный режим выполнения упакованных операций

SSE во всех трёх каналах исполнения; - увеличена ширина и пропускная способность доступа к L1-кэшу;

- введён 64-битный режим EM64T (x86-64), а также дополнительный режим SSE4.

Однако, наряду с усовершенствованиями, в микроархитектуре нового процессора P8 остались некоторые недостатки предыдущих архитектур. Часть этих недостатков являются количественными ограничениями «компромиссного» типа, другие, по всей видимости, носят более принципиальный характер, связанный с базовыми ограничениями данной микроархитектуры. Перечислим обнаруженные недостатки в порядке возрастания их важности (с точки зрения автора):

- умножения в режиме x87 выполняется в половинном темпе;

- переходы выполняются в темпе не более одной операции за такт;

- не очень эффективно реализованы инструкции работы с флагом переноса CF (ADC, SBB), необходимые для работы с числами произвольной длины;

- сохранилась проблема, связанная с «частичной записью флагов», главным образом относящаяся к флагу переноса CF;

- сохранилось ограничение на число считываний архитектурных регистров в каждом такте на этапе переименования и выделения регистров (Register read stall);

- обращение к кэшу данных ограничивается темпом «одна загрузка плюс одна выгрузка за такт».

Из перечисленных проблем, только последняя (темп обращений к кэшу) поддаётся количественному анализу и может рассматриваться как некоторое ограничение производительности. Ещё одна проблема (число считываний архитектурных регистров) является весьма специфичной, поскольку связана с тонкими особенностями организации регистровых файлов. Детали этой организации доподлинно не известны. Специально подобранными тестами можно добиться значительного снижения темпа выполнения инструкций (до одной за такт), однако такие тесты весьма экзотичны и не соответствуют реальным программам. Судя по результатам различных замеров производительности (особенно по чрезвычайно высоким показателям набора тестов SPECint2000), данный эффект не очень сильно проявляется на практике.

Таким образом, можно заключить, что изначально удачную (концептуально) динамическую архитектуру P6 наконец-то наполнили адекватным содержанием, добавив в неё в процессе развития (P6 — P6+ — P8) множество интересных нововведений (слияние микроопераций, макро-слияние, работа с аппаратным стеком, механизм устранения неоднозначностей при обращении в память, режим x86-64 и проч.).

В настоящий момент ещё нет данных о дальнейшем развитии микроархитектур процессоров компании Intel. Известно лишь, что в ближайшие два года процессоры всех классов (мобильные, десктопные и серверные) будут базироваться на архитектуре Intel Core (P8), а основное развитие будет идти в направлении увеличения числа ядер на кристалле и усовершенствования внешних интерфейсов процессора.

Процессоры компании AMD

Развитие современных микроархитектур в компании AMD началось с создания в 1999 г. процессора Athlon (K7). Это был первый полноценный суперскалярный конвейерный микропроцессор с внеочередным исполнением операций, разработанный в компании. В микроархитектуре процессора K7 нашли отражение все те основные принципы, которые были до этого реализованы в процессоре Intel Pentium Pro (P6). Однако конкретные подходы разработчиков AMD отличались большей простотой и изобретательностью, направленной на снижение сложности процессора и увеличение его производительности. Разработчики частично пожертвовали гибкостью и динамическими элементами архитектуры, но при этом уделили внимание скорости выполнения многих инструкций (в особенности операций арифметики с плавающей точкой), значительно увеличили размер кэшей 1-го уровня (ограничившись при этом низким уровнем ассоциативности) и ввели важный механизм объединения адресной и арифметической микрооперации в один общий МОП (Load-Op, Op-Store, Load-Op-Store). Благодаря этому процессор K7 сразу обогнал по производительности своего конкурента P-III, и в дальнейшем, с появлением процессора P-4, достойно ему противостоял на некоторых применениях. В процессе своего развития процессор K7 подвергался усовершенствованиям.

Следующий процессор компании Athlon 64 / Opteron (K8), увидевший свет в 2003 г., мало отличается от своего предшественника K7 по микроархитектуре. При его создании основной упор был сделан на две ключевые технологии: 64-битный режим целочисленной и адресной арифметики AMD64 (x86-64), и интегрированный контроллер оперативной памяти, встроенный в процессорный чип. Создание расширенной архитектуры x86-64 позволило снять ограничения по адресации памяти, сдерживающие развитие десктопных процессоров, а реализация встроенного контроллера существенно снизила латентность доступа к оперативной памяти, тем самым, дав значительный прирост в производительности на многих задачах. В дальнейшем архитектура x86-64 стала стандартной и была реализована в процессорах Intel P-4E и P8. Внедрение встроенного контроллера памяти в процессорах компании Intel также предполагается в ближайшие годы.

Помимо этих ключевых технологий, в процессоре K8 имеется ряд менее значимых отличий от K7:

- усовершенствован декодер машинных инструкций, большинство «сложных» инструкций, порождающих 2 МОПа, переведены в разряд «простых»;

- добавлены режимы SSE2 и (чуть позднее) SSE3;

- несколько улучшена подсистема предсказания переходов;

- увеличена длина очередей планировщика, проведены некоторые модификации в подсистеме внеочередного исполнения и в функциональных устройствах;

- расширена шина L2-кэша и уменьшено время доступа;

- обеспечено комплексирование в многопроцессорные конфигурации через интерфейс HyperTransport без использования внешней логики (чипсета);

- реализована двухъядерность с раздельными L2-кэшами и общим контроллером памяти (в процессоре K8 X2).

Кроме перечисленного, можно подчеркнуть ещё несколько отличительных черт процессоров K7/K8, способствующих повышению их производительности:

- частичное предекодирование инструкций перед помещением в I-кэш;

- возможность выполнения двух загрузок из L1-кэша за такт;

- малая длина конвейера непредсказанного перехода благодаря разделению подсистем целочисленно-адресной арифметики (ALU/AGU) и арифметики с плавающей точкой (FPU);

- наличие трёх симметричных устройств для выполнения целочисленных и адресных операций ALU/AGU.

Однако в архитектуре процессора K8 имеется и ряд недостатков, часть из которых обусловлена базовыми ограничениями микроархитектуры:

- статическое разбиение потока МОПов на группы по 3 элемента с привязкой очередей и функциональных устройств ALU/AGU к позициям этих элементов;

- слабая система предсказания переходов, использующая устаревшие алгоритмы;

- недостаточно совершенная аппаратная предвыборка из памяти;

- отсутствие механизмов переупорядочения обращений к памяти;

- взаимно эксклюзивная организация кэшей, ограничивающая скорость выборки из L2-кэша и увеличивающая время доступа;

- недостаточная ассоциативность L1-кэшей, снижающая их эффективность.

В целом процессор K8 составил хорошую конкуренцию процессорам P-4 и P-4E. Благодаря меньшей длине конвейеров и более эффективной реализации многих инструкций он оказался не столь требователен к оптимизации кодов и в ряде применений имеет более высокую производительность. Особенно это относится к игровым программам и некоторым десктопным приложениям. В настоящее время производится перевод процессоров K8 на использование оперативной памяти DDR2, обладающей повышенной пропускной способностью. Этот переход позволит несколько повысить производительность, особенно для двухъядерных вариантов (K8 X2). Дополнительным достоинством нынешних вариантов процессоров K8 является относительно невысокое энергопотребление и тепловыделение (в сравнении с процессорами P-4).

Однако K8 значительно уступает новому процессору P8 (Intel Core), особенно игровых и десктопных применениях. Это отставание наиболее сильно заметно на тестовом наборе SPECint2000, а также (в меньшей степени) на наборе SPECfp2000. Превосходство процессора P8 в производительности обусловлено в первую очередь динамической организацией его архитектуры, имеющей увеличенную ширину запуска и обработки инструкций, полночастотным выполнением упакованных 128-битных операций SSE, увеличенным размером L2-кэша, более совершенным предсказателем переходов и улучшенной подсистемой предвыборки данных. Поскольку процессор P8 построен на примерно тех же фундаментальных архитектурных принципах, что и K8, и имеет сопоставимую с ним длину конвейера, он не обладает «недостатками» процессора P-4 и поэтому страдает от недостаточной оптимизации кодов не в большей степени, чем K8. Кроме того, процессор P8 имеет пониженное энергопотребление и улучшенные механизмы управления питанием.

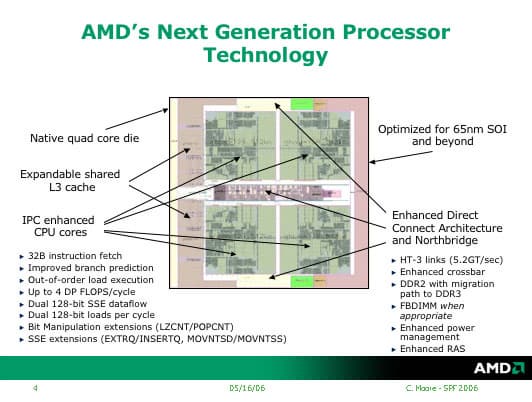

В связи с появлением столь серьёзного конкурента, компания AMD объявила о планах создания к середине 2007 г. нового процессора с улучшенной и расширенной микроархитектурой, известного под названием K8L (Рис. 12).

Рис. 12

В целом новый процессор повторяет идеологию своего предшественника, однако имеет множество усовершенствований и отличительных признаков. Наиболее важными из них являются:

- реализация полночастотного 128-битного режима выполнения упакованных операций SSE (в двух каналах исполнения);

- увеличение ширины и пропускной способности доступа к L1-кэшу — теперь в каждом такте могут выполняться две 128-битные загрузки за такт либо одна загрузка и одна выгрузка (в процессоре P8 — только одна такая загрузка и одна выгрузка);

- увеличение длины выборки из кэша инструкций до 32 байтов;

- усовершенствование механизма предсказания переходов, добавление предсказателя косвенных переходов;

- появление механизма внеочередной выборки данных из памяти;

- некоторое расширение системы команд.

Кроме того, изменилась структура и внешние интерфейсы процессора. Теперь базовый вариант содержит 4 процессорных ядра, имеющих раздельные L2-кэши по 512 Кбайт и общий кэш 3-го уровня размером 2 Мбайта (в последующих версиях процессора L3-кэш увеличится). Коммуникационные интерфейсы HyperTransport, используемые для ввода-вывода и для объединения в многопроцессорную систему с общей памятью, перешли на стандарт HT-3.0, обеспечивающий повышенную скорость обменов и улучшенную функциональность. Максимальная частота интерфейсов выросла до 2.6 ГГц, а пиковая скорость передачи данных — до 10.4 Гбайт/с (в каждом направлении). Число интерфейсов увеличилось с трёх до четырёх, что позволяет реализовывать полносвязные системы из 4 процессоров (сокетов) и повысить степень интеграции систем из 8 процессоров (сокетов).

В остальном микроархитектура процессора K8L повторяет архитектуру K8: сохранилась ширина выборки и обработки инструкций, равная трём, по-прежнему производится разбиение потока МОПов на группы по 3 элемента со статической привязкой очередей и устройств ALU/AGU к позициям этих элементов, не претерпела особых изменений система внеочередного исполнения операций (с разделением на подсистемы ALU/AGU и FPU). Также нет упоминаний о том, увеличилась ли ассоциативность кэшей 1-го уровня (увеличение уровня ассоциативности с 2 до 4 позволило бы заметно повысить эффективность использования этих кэшей).

Таким образом, новый процессор сохранил ряд недостатков предыдущей архитектуры. Также неоднозначным является решение уменьшить размер L2-кэша у каждого ядра до 512 Кбайт и объединить ядра на следующем, третьем уровне кэша. Размер L3-кэша (2 Мбайта) тоже весьма невелик — правда, он, по всей вероятности, реализован эксклюзивно по отношению к L2-кэшам, и поэтому его эффективный размер при тяжёлой нагрузке может увеличиться на сумму размеров L2-кэшей (то есть до 4 Мбайт).

Самым принципиальным отличием процессорного ядра K8L от ядра K8 является удвоение скорости работы блока арифметики с плавающей точкой (для упакованных режимов SSE). Идея введения полночастотной 128-битной обработки SSE-регистров витала в воздухе в течение ряда лет и рассматривалась как естественный путь развития микроархитектуры процессора K8. И, наконец, она будет реализована — правда, лишь через год после внедрения этой идеи в процессор Intel Core (P8).

Упомянутые выше недостатки и ограничения микроархитектуры K8L (в первую очередь невысокая ширина обработки и недостаточно «динамическая» реализация целочисленной арифметики ALU в сочетании с относительно небольшим размером кэшей верхних уровней) не позволят новому процессору превзойти конкурирующую архитектуру Intel Core (P8) на целочисленных и игровых применениях — так что для таких задач следует ожидать отставания в производительности. Однако на ряде применений с активным использованием арифметики с плавающей точкой процессор K8L может достойно противостоять конкуренту, а в ряде случаев и превосходить его. Небольшое превосходство на таких задачах может быть обеспечено благодаря высокой эффективности встроенного контроллера памяти и большему размеру L1-кэша в сочетании с возможностью выполнять до двух загрузок из кэша за такт. Эти факторы позволят компенсировать общие недостатки архитектуры на достаточно регулярных кодах. Например, на задаче перемножения больших матриц можно ожидать достижения производительности на уровне 85% от пиковой, против оценки на уровне 80% для процессора P8 (при одинаковой тактовой частоте и сопоставимых размерах кэшей верхних уровней). Также можно ожидать паритета или небольшого превосходства процессора K8L на наборе тестов SPECfp2000.

К сожалению, в нынешней архитектуре x86 отсутствуют адекватные средства для работы с не выровненными операндами в упакованном режиме SSE2, что затрудняет использование этого режима для обработки групп массивов, не выровненных друг относительно друга с 16-байтной кратностью. Данное ограничение снижает вычислительный потенциал обеих конкурирующих архитектур — и P8, и K8L. Появление таких средств в будущих расширениях режима SSE создало бы дополнительную интригу и позволило бы более отчётливо выявить резервы каждой архитектуры.

Таким образом, противостояние процессоров компаний Intel и AMD в настоящее время перешло из плоскости войны революционных концепций и новаций (P-4 против K7/K8) в плоскость борьбы эволюционных расширений и реализаций (P8 против K8/K8L). В рамках этого противостояния компания AMD, безусловно, должна будет разработать новую, продвинутую микроархитектуру, более широкую и динамическую по своей природе. В сочетании с удачными наработками из предыдущих поколений процессоров (гибкий механизм предварительного декодирования инструкций, эффективные функциональные устройства, широкий доступ к L1-кэшам, низколатентный встроенный контроллер памяти и быстрые интерфейсы HyperTransport) это позволит будущей архитектуре достигнуть всестороннего паритета либо превосходства над процессорами конкурента.

Процессоры компании IBM

Компания IBM развивала процессорные микроархитектуры главным образом для серверных применений. Нынешнее поколение архитектуры было разработано в 2001 г. и реализовано в серверном процессоре Power4. Позднее был создан десктопный вариант PowerPC 970, отличающийся добавлением векторного блока 32-битной арифметики с плавающей точкой VMX, а также уменьшенным размером L2-кэша и изменённым внешним интерфейсом. Этот процессор используется в персональных компьютерах компании Apple, а также в модулях компании IBM для построения вычислительных кластеров и небольших серверов. В настоящее время выпускается двухъядерный вариант процессора PPC970MP.

Процессор PPC970 имеет очень хороший потенциал пиковой производительности, особенно для арифметики с плавающей точкой. Этот потенциал основан на увеличенной ширине выборки и исполнения инструкций (4-5 за такт) вкупе с большим числом очередей внеочередного исполнения, портов запуска и функциональных устройств. Поэтому для регулярных кодов с хорошим планированием инструкций PPC970 способен достигать высокой скорости вычислений.

С другой стороны, в микроархитектуре процессора имеется множество упрощений, которые делают её недостаточно «динамической». Также имеется ряд недостатков в реализации кэшей и функциональных устройств. Приведём список основных ограничений и недостатков микроархитектуры PPC970:

- статическое разбиение потока МОПов на группы по 4-5 элементов с привязкой очередей и функциональных устройств к позициям этих элементов;

- наличие множества ограничительных условий, снижающих число МОПов в формируемой группе (на выходе из декодера);

- недостаточно эффективная реализация L1-кэшей, имеющих низкий уровень ассоциативности и слишком большой размер блока;

- завышенное время выполнения предсказанного перехода (3 такта против 2 тактов у других процессоров);

- высокая латентность выполнения целочисленных операций (2 такта) и операций с плавающей точкой (6 тактов);

- недостаточная пропускная способность памяти из-за ограниченной скорости шины.

Наиболее важным является первый недостаток — статическая привязка очередей и устройств к позициям инструкций. Такая привязка может привести к несбалансированной загрузке однотипных устройств и заметному снижению производительности. Большое время выполнения переходов и арифметико-логических инструкций также снижает производительность на кодах с нерегулярной структурой. Таким образом, процессор PPC970 не очень хорошо сбалансирован и демонстрирует недостаточно высокую производительность на большинстве применений, несмотря на наличие у него хорошего потенциала. Это явилось одной из причин, по которой компания Apple в настоящее время отказывается от использования процессора PPC970 в своих компьютерах и переходит на процессоры архитектуры Intel Core (P8).

Однако серверные варианты процессора — Power4 и Power5 — нашли широкое применение в соответствующих нишах. Эти процессоры имеют двухъядерную организацию с большими интегрированными L2-кэшами, общими для обоих ядер. Конструктивно процессоры Power4 и Power5 объединяются на многочиповой сборке, содержащей 4 процессорных кристалла и кэш 3-го уровня большого объёма. Процессоры связаны друг с другом, с L3-кэшами и с оперативной памятью очень быстрыми шинами. Благодаря этому многопроцессорные системы с общей памятью, построенные на этих процессорах, достигают рекордной производительности на научно-технических задачах, обладающих высокой регулярностью. Наилучших результатов достигает процессор Power5, который не очень значительно отличается от своих предшественников (Power4 и PPC970) по микроархитектуре, однако имеет вынесенный индивидуальный контроллер памяти. Благодаря этому подсистема памяти обладает очень высокой суммарной пропускной способностью, что снижает потери на обращения в память при выполнении большого числа задач.

В настоящее время компания IBM разрабатывает новую, более совершенную микроархитектуру Power6. Эта архитектура будет основана на значительном повышении тактовой частоты — в 1.5 раза и более в сравнении с конкурирующими процессорами. Такое повышение частоты будет обеспечено в первую очередь за счёт применения современных электронных технологий и усовершенствования схемной логики, а также за счёт некоторого увеличения длины конвейеров. Предполагается, что удлинение конвейеров будет достаточно умеренным и не приведёт к необходимости введения неоднозначных «революционных» новшеств в микроархитектуру (как в процессоре Intel P-4). Поэтому компания IBM ожидает пропорционального роста производительности процессора с тактовой частотой. Такому росту производительности также будет способствовать реализация эффективного L1-кэша размером 64 Кбайта с высоким уровнем ассоциативности, низколатентное выполнение арифметико-логических операций и наличие (как и в предыдущих процессорах Power4/5) сдвоенного блока арифметики с плавающей точкой, обеспечивающего выполнение четырёх 64-битных операций за такт.

Новый процессор также будет иметь индивидуальные контроллеры оперативной памяти с высокой пропускной способностью, быстрые межпроцессорные шины и увеличенные кэши верхних уровней.

Несмотря на то, что Power6 ориентирован в первую очередь против серверного процессора Intel Itanium (IA-64), его появление в 2007 г. должно обострить конкурентную борьбу в сфере десктопных процессоров и стимулировать дальнейшее повышение их производительности. Этому должно способствовать также и предполагаемое создание «облегчённого» десктопного процессора на базе новой архитектуры (G6), который придёт на смену нынешнему процессору PPC970 (G5).

Будем надеяться, что процессор Power6 даст новый импульс развитию высокочастотных микроархитектур — только на этот раз не за счёт чрезмерного увеличения длины конвейеров вместе с сопутствующими неприятными эффектами, а посредством тщательного совершенствования и оптимизации схемной логики при сохранении достаточно консервативных и устоявшихся микроархитектурных принципов.

Список литературы

- O. Bessonov, D. Fougere, B. Roux. Development of efficient computational kernels and linear algebra routines for out-of-order superscalar processors. Future Generation Computer Systems, V.21, No.5, 2005, pp.743-748.

- A. Fog. How to optimize for the Pentium family of microprocessors. 2004.

- M. Milenkovic, A. Milenkovic, J. Kulick. Demystifying Intel Branch Predictors. Proceedings of the Workshop on Duplicating, Deconstructing and Debunking, 2002.

- О. Бессонов. Pentium 4: Мистический и загадочный Trace-кэш. Ф-Центр, 2005.

- Я. Керученько, Ю. Малич, В. Левченко. Replay: неизвестные особенности функционирования ядра Netburst. Ф-Центр, 2005.

- В. Картунов. Prescott: Последний из могикан? (Pentium 4: от Willamette до Prescott). Ф-Центр, 2005.

- О. Бессонов. Новое вино в старые мехи. Conroe: внук процессора Pentium III, племянник архитектуры NetBurst? iXBT.com, 2005.

- О. Бессонов. Двухъядерный процессор Yonah: уже не Pentium III, ещё не Conroe. iXBT.com, 2006.

- H.H. Sean Lee. P6 & NetBurst Microarchitecture. School of ECE, Georgia Institute of Technology, 2003.

- IA-32 Intel Architecture Optimization Reference Manual. Intel, 2006.

- IA-32 Intel Architecture Software Developer's Manual. Intel, 2006.

- Intel Architecture Optimization Reference Manual. Intel, 1999.

- J. Keshava, V. Pentkovski. Pentium III Processor Implementation Tradeoffs. Intel Technology Journal, V.3, Q2, 1999.

- G. Hinton et al. The Microarchitecture of the Pentium 4 Processor. Intel Technology Journal, V.5, Q1, 2001.

- S. Gochman et al. The Intel Pentium M Processor: Microarchitecture and Performance. Intel Technology Journal, V.7, Issue 2, 2003.

- S. Gochman et al. Introduction to Intel Core Duo Processor Architecture. Intel Technology Journal, V.10, Issue 2, 2006.

- D. Boggs et al. The Microarchitecture of the Intel Pentium 4 Processor on 90nm Technology. Intel Technology Journal, V.8, Issue 1, 2004.

- B. Valentine. Inside the Intel Core Microarchitecture. Intel Developer Forum, 2006.

- B. Inkley. Inside the Intel Core Microarchitecture. Intel Developer Forum, 2006.

- D. Kanter. Intel's Next Generation Microarchitecture Unveiled. Real World Technologies, 2006.

- Instruction length decoder for generating output length indicia to identity boundaries between variable length instructions. United State Patent 5,758,116, 1998.

- Software Optimization Guide for AMD64 Processors. AMD, 2005.

- В. Картунов. Детальное исследование архитектуры AMD64. iXBT.com, 2003.

- H. de Vries. Understanding the detailed Architecture of AMD's 64 bit Core. Chip-Architect, 2003.

- D. Kanter. AMD's K8L and 4x4 Preview. Real World Technologies, 2006.

- J. Tendler et al. POWER4 system microarchitecture. IBM Journal of Research and Development, V.46, No.1, 2002.

- Tom R. Halfhill. IBM Trims Power4, Adds ALTIVEC. 64-Bit PowerPC 970 Targets Entry-Level Servers and Desktops. Microprocessor Report, Oct.28, 2002.

- J. Stokes. Inside the PowerPC 970. Part II: The Execution Core. Ars Technica, 2003.

- С. Гарматюк. Современные десктопные процессоры архитектуры x86: общие принципы работы. iXBT.com, 2006.