Часть 26: Высокоскоростные модули OCZ серий Titanium и SLI-Ready (PC2-6400, PC2-7200 и PC2-8000)

Мы продолжаем изучение важнейших характеристик высокоскоростных модулей DDR2 с помощью универсального тестового пакета RightMark Memory Analyzer. Сегодня мы рассмотрим высокоскоростные предложения от компании OCZ — три двухканальных 2-ГБ комплекта модулей памяти серий Titanium и SLI-Ready скоростных категорий PC2-6400, PC2-7200 и PC2-8000:

- OCZ DDR2 PC2-6400 Titanium EPP-Ready (OCZ2T8002GK, DDR2-800 4-4-4-1T)

- OCZ DDR2 PC2-7200 SLI-Ready Edition (OCZ2N900SR2GK, DDR2-900 4-4-3-2T)

- OCZ DDR2 PC2-8000 Titanium Alpha VX2 (OCZ2TA1000VX22GK, DDR2-1000 4-4-4-2T)

Информация о производителе модуля

Производитель модуля: OCZ Technology

Производитель микросхем модуля: неизвестен

Сайт производителя модуля: www.ocztechnology.com/products/ddr2/

Внешний вид модулей

OCZ DDR2 PC2-6400

OCZ DDR2 PC2-7200

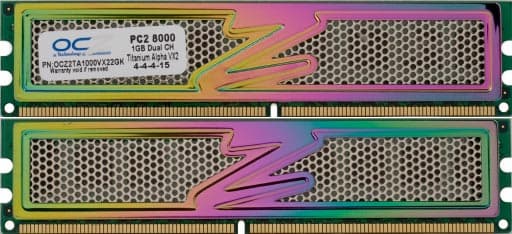

OCZ DDR2 PC2-8000

Part Number модулей

Руководство по расшифровке Part Number модулей памяти DDR2 на сайте производителя отсутствует (в ходе его изучения было обнаружено лишь устаревшее руководство, посвященное модулям памяти типа DDR). Поэтому ограничимся лишь кратким описанием модулей, представленным на страницах соответствующих продуктов.

OCZ DDR2 PC2-6400

Модули OCZ DDR2 PC2-6400 Titanium EPP-Ready поддерживают стандарт EPP, что позволяет достичь оптимальной производительности модулей на материнских платах с чипсетами NVIDIA nForce 590 SLI. Содержимое EPP запрограммировано на режим DDR2-800 с достаточно низкими таймингами 4-4-4-1T, т.е. модули способны функционировать при задержках командного интерфейса 1T (1 команда/1 такт), что значительно увеличивает производительность подсистемы памяти. Модули оснащены теплоотводами XTC (Xtreme Thermal Convection) с титановым покрытием, обеспечивающими эффективный отвод тепла.

OCZ DDR2 PC2-7200

Модули OCZ DDR2 PC2-7200 SLI-Ready Edition также поддерживают стандарт EPP, при этом содержимое данной части микросхемы SPD запрограммировано на режим DDR2-900 со схемой таймингов 4-4-3. Как утверждает производитель, данные модули оснащены эксклюзивной системой теплоотведения NVIDIA XTC (с точки зрения, как эффективности, так и внешнего вида, «соответствующего» уровню производительности модулей).

OCZ DDR2 PC2-8000

В отличие от первых двух представителей, поддержка стандарта EPP в модулях OCZ DDR2 PC2-8000 Titanium Alpha VX2 отсутствует. Модули принадлежат особому семейству модулей Voltage Xtreme, рассчитанных на работу при высоком питающем напряжении (что позволяет достичь скоростей, недоступных при обычном уровне напряжения). Данная модель рассчитана на режим DDR2-1000 при задержках 4-4-4, что достигается за счет поднятия питающего напряжения до 2.3В и позиционируется как high-end решение для экстремальных геймеров и оверклокеров. Теплоотвод модулей XTC с применением титанового покрытия, устойчивого к царапинам, также является эксклюзивным решением, на сей раз — по своей цветовой гамме (см. фото). Каждый модуль Titanium Alpha имеет уникальную цветовую гамму и изменяет свой оттенок цвета в зависимости от освещения и угла обзора.

Данные микросхемы SPD модулей

Описание общего стандарта SPD:

Описание специфического стандарта SPD для DDR2:

Описание стандарта EPP:

OCZ DDR2 PC2-6400

| Параметр | Байт | Значение | Расшифровка |

|---|---|---|---|

| Фундаментальный тип памяти | 2 | 08h | DDR2 SDRAM |

| Общее количество адресных линий строки модуля | 3 | 0Eh | 14 (RA0-RA13) |

| Общее количество адресных линий столбца модуля | 4 | 0Ah | 10 (CA0-CA9) |

| Общее количество физических банков модуля памяти | 5 | 61h | 2 физических банка |

| Внешняя шина данных модуля памяти | 6 | 40h | 64 бит |

| Уровень питающего напряжения | 8 | 05h | SSTL 1.8V |

| Минимальная длительность периода синхросигнала (tCK) при максимальной задержке CAS# (CL X) | 9 | 25h | 2.50 нс (400.0 МГц) |

| Тип конфигурации модуля | 11 | 00h | Non-ECC |

| Тип и способ регенерации данных | 12 | 82h | 7.8125 мс — 0.5x сокращенная саморегенерация |

| Ширина внешнего интерфейса шины данных (тип организации) используемых микросхем памяти | 13 | 08h | x8 |

| Ширина внешнего интерфейса шины данных (тип организации) используемых микросхем памяти ECC-модуля | 14 | 00h | Не определено |

| Длительность передаваемых пакетов (BL) | 16 | 0Ch | BL = 4, 8 |

| Количество логических банков каждой микросхемы в модуле | 17 | 04h | 4 |

| Поддерживаемые длительности задержки CAS# (CL) | 18 | 38h | CL = 5, 4, 3 |

| Минимальная длительность периода синхросигнала (tCK) при уменьшенной задержке CAS# (CL X-1) | 23 | 30h | 3.00 нс (333.3 МГц) |

| Минимальная длительность периода синхросигнала (tCK) при уменьшенной задержке CAS# (CL X-2) | 25 | 37h | 3.70 нс (270.3 МГц) |

| Минимальное время подзарядки данных в строке (tRP) | 27 | 32h | 12.5 нс 5.00, CL = 5 4.17, CL = 4 3.37, CL = 3 |

| Минимальная задержка между активизацией соседних строк (tRRD) | 28 | 28h | 10.0 нс 4.00, CL = 5 3.33, CL = 4 2.70, CL = 3 |

| Минимальная задержка между RAS# и CAS# (tRCD) | 29 | 32h | 12.5 нс 5.00, CL = 5 4.17, CL = 4 3.37, CL = 3 |

| Минимальная длительность импульса сигнала RAS# (tRAS) | 30 | 25h | 37.0 нс 14.80, CL = 5 12.33, CL = 4 10.00, CL = 3 |

| Емкость одного физического банка модуля памяти | 31 | 80h | 512 МБ |

| Период восстановления после записи (tWR) | 36 | 3Ch | 15.0 нс 6.00, CL = 5 5.00, CL = 4 4.05, CL = 3 |

| Внутренняя задержка между командами WRITE и READ (tWTR) | 37 | 1Eh | 7.5 нс 3.00, CL = 5 2.50, CL = 4 2.02, CL = 3 |

| Внутренняя задержка между командами READ и PRECHARGE (tRTP) | 38 | 1Eh | 7.5 нс 3.00, CL = 5 2.50, CL = 4 2.02, CL = 3 |

| Минимальное время цикла строки (tRC) | 41, 40 | 37h, 00h | 55.0 нс 22.00, CL = 5 18.33, CL = 4 14.86, CL = 3 |

| Период между командами саморегенерации (tRFC) | 42, 40 | 69h, 00h | 105.0 нс 42.00, CL = 5 35.00, CL = 4 28.38, CL = 3 |

| Максимальная длительность периода синхросигнала (tCKmax) | 43 | 80h | 8.0 нс |

| Номер ревизии SPD | 62 | 23h | Ревизия 2.3(?) |

| Контрольная сумма байт 0-62 | 63 | BFh | 191 (верно) |

| Идентификационный код производителя по JEDEC | 64-71 | 7Fh, 7Fh, 7Fh, 7Fh, B0h | OCZ |

| Part Number модуля | 73-90 | — | OCZ2T8001G |

| Дата изготовления модуля | 93-94 | 06h, 26h | 2006 год, 38 неделя |

| Серийный номер модуля | 95-98 | 00h, 00h, 00h, 00h | Не определено |

По данным SPD, поддерживаемые значения задержки сигнала CAS# составляют 5, 4 и 3. Первому значению (CL X = 5) соответствует период синхросигнала 2.5 нс (частота 400 МГц), т.е. режим DDR2-800. Схема таймингов для этого случая не полностью представляется целыми значениями и может быть записана в виде 5-5-5-14.8, что с учетом наиболее вероятного округления в большую сторону соответствует стандартной схеме 5-5-5-15. Уменьшенной величине задержки CAS# (CL X-1 = 4) соответствует режим DDR2-667 (время цикла 3.0 нс, частота 333.3 МГц) с нецелой схемой таймингов 4-4.17-4.17-12.33, которую с учетом округления можно записать в виде 4-5-5-13. Наконец, дважды уменьшенной величине задержки CAS# (CL X-2 = 3) соответствует несколько ошибочная, но распространенная запись режима DDR2-533 со временем цикла 3.7 нс (частота 270.3 МГц) вместо номинального значения 3.75 нс (частота 266.7 МГц). Схема таймингов для этого случая — 3-3.37-3.37-10, с учетом округления — 3-4-4-10.

Идентификационный код производителя, дата изготовления и Part Number модуля указаны верно, в то время как информация о серийном номере модуля отсутствует. К тому же, несколько настораживает странное значение ревизии SPD 23h, формально соответствующее несуществующему номеру ревизии стандарта «2.3».

Поскольку данные модули поддерживают расширение EPP, рассмотрим теперь информацию, содержащуюся в этой «нестандартной» части SPD, представленной байтами 99-127 содержимого SPD.

| Параметр | Байт(ы) (биты) | Значение | Расшифровка |

|---|---|---|---|

| Строка идентификации EPP | 99-101 | 4E566Dh | Есть поддержка SPD EPP |

| Тип профилей EPP | 102 | A1h | Сокращенные профили |

| Профиль оптимальной производительности | 103 (1:0) | 00h | Профиль 0 |

| Используемые профили | 103 (7:4) | 01h | Профиль 0: присутствует Профиль 1: отсутствует Профиль 2: отсутствует Профиль 3: отсутствует |

| Профиль №0 | |||

| Уровень питающего напряжения | 104 (6:0) | 08h | 2.0 V |

| Задержка передачи адреса (Addr CMD rate) | 104 (7) | 00h | 1T |

| Время цикла (tCK) | 105 | 25h | 2.50 нс (400.0 МГц) |

| Задержка CAS# (tCL) | 106 | 10h | 4 |

| Минимальная задержка между RAS# и CAS# (tRCD) | 107 | 28h | 10.0 нс (4.0) |

| Минимальное время подзарядки данных в строке (tRP) | 108 | 28h | 10.0 нс (4.0) |

| Минимальная длительность импульса сигнала RAS# (tRAS) | 109 | 25h | 37.0 нс (14.8) |

Информация EPP представлена в виде сокращенных профилей, максимально возможное количество которых — 4, тогда как реально присутствуют данные лишь о первом из этих профилей (профиль №0), который, естественно, отмечен как «оптимальный». Информация, содержащаяся в этом сокращенном профиле, весьма немногочисленна и полностью представлена в приведенной выше таблице. Это данные о питающем напряжении модулей — 2.0 V, величине задержек командного интерфейса (1T), времени цикла (2.5 нс, частота шины памяти 400 МГц, режим DDR2-800) и стандартных таймингах (4-4-4-14.8, с учетом округления 4-4-4-15). Дополнительные параметры тонкой настройки временных и электрических характеристик функционирования подсистемы памяти в содержимом «сокращенного» профиля EPP отсутствуют, что, на наш взгляд, ставит под сомнение его основные преимущества. Вероятно, производитель модулей просто не уделил должного внимания тонкой настройке этих характеристик. К чему это привело, мы увидим дальше, в ходе нашего исследования модулей, а пока перейдем к рассмотрению SPD следующего представителя.

OCZ DDR2 PC2-7200

| Параметр | Байт | Значение | Расшифровка |

|---|---|---|---|

| Фундаментальный тип памяти | 2 | 08h | DDR2 SDRAM |

| Общее количество адресных линий строки модуля | 3 | 0Eh | 14 (RA0-RA13) |

| Общее количество адресных линий столбца модуля | 4 | 0Ah | 10 (CA0-CA9) |

| Общее количество физических банков модуля памяти | 5 | 61h | 2 физических банка |

| Внешняя шина данных модуля памяти | 6 | 40h | 64 бит |

| Уровень питающего напряжения | 8 | 05h | SSTL 1.8V |

| Минимальная длительность периода синхросигнала (tCK) при максимальной задержке CAS# (CL X) | 9 | 25h | 2.50 нс (400.0 МГц) |

| Тип конфигурации модуля | 11 | 00h | Non-ECC |

| Тип и способ регенерации данных | 12 | 82h | 7.8125 мс — 0.5x сокращенная саморегенерация |

| Ширина внешнего интерфейса шины данных (тип организации) используемых микросхем памяти | 13 | 08h | x8 |

| Ширина внешнего интерфейса шины данных (тип организации) используемых микросхем памяти ECC-модуля | 14 | 00h | Не определено |

| Длительность передаваемых пакетов (BL) | 16 | 0Ch | BL = 4, 8 |

| Количество логических банков каждой микросхемы в модуле | 17 | 04h | 4 |

| Поддерживаемые длительности задержки CAS# (CL) | 18 | 38h | CL = 5, 4, 3 |

| Минимальная длительность периода синхросигнала (tCK) при уменьшенной задержке CAS# (CL X-1) | 23 | 3Dh | 3.75 нс (266.7 МГц) |

| Минимальная длительность периода синхросигнала (tCK) при уменьшенной задержке CAS# (CL X-2) | 25 | 00h | Не определено |

| Минимальное время подзарядки данных в строке (tRP) | 27 | 32h | 12.5 нс 5.00, CL = 5 3.33, CL = 4 Не определено, CL = 3 |

| Минимальная задержка между активизацией соседних строк (tRRD) | 28 | 1Eh | 7.5 нс 3.00, CL = 5 2.00, CL = 4 Не определено, CL = 3 |

| Минимальная задержка между RAS# и CAS# (tRCD) | 29 | 32h | 12.5 нс 5.00, CL = 5 3.33, CL = 4 Не определено, CL = 3 |

| Минимальная длительность импульса сигнала RAS# (tRAS) | 30 | 25h | 37.0 нс 14.80, CL = 5 9.87, CL = 4 Не определено, CL = 3 |

| Емкость одного физического банка модуля памяти | 31 | 80h | 512 МБ |

| Период восстановления после записи (tWR) | 36 | 3Ch | 15.0 нс 6.00, CL = 5 4.00, CL = 4 Не определено, CL = 3 |

| Внутренняя задержка между командами WRITE и READ (tWTR) | 37 | 1Eh | 7.5 нс 3.00, CL = 5 2.00, CL = 4 Не определено, CL = 3 |

| Внутренняя задержка между командами READ и PRECHARGE (tRTP) | 38 | 1Eh | 7.5 нс 3.00, CL = 5 2.00, CL = 4 Не определено, CL = 3 |

| Минимальное время цикла строки (tRC) | 41, 40 | 37h, 00h | 55.0 нс 22.00, CL = 5 14.86, CL = 4 Не определено, CL = 3 |

| Период между командами саморегенерации (tRFC) | 42, 40 | 69h, 00h | 105.0 нс 42.00, CL = 5 28.38, CL = 4 Не определено, CL = 3 |

| Максимальная длительность периода синхросигнала (tCKmax) | 43 | 80h | 8.0 нс |

| Номер ревизии SPD | 62 | 12h | Ревизия 1.2 |

| Контрольная сумма байт 0-62 | 63 | 2Ah | 42 (верно) |

| Идентификационный код производителя по JEDEC | 64-71 | 7Fh, 7Fh, 7Fh, 7Fh, B0h | OCZ |

| Part Number модуля | 73-90 | — | OCZ2N900SR1G |

| Дата изготовления модуля | 93-94 | 00h, 00h | Не определено |

| Серийный номер модуля | 95-98 | 00h, 00h, 00h, 00h | Не определено |

Поддерживаемые значения задержки сигнала CAS# — 5, 4 и 3, однако значения периодов синхросигнала указаны лишь для первых двух значений: основного (CL X = 5) и уменьшенного (CL X-1 = 4). Первому значению (CL X = 5) соответствует период синхросигнала 2.5 нс (частота 400 МГц), т.е. режим DDR2-800. Схема таймингов для этого случая может быть записана в виде нецелых значений 5-5-5-14.8, с учетом наиболее вероятного округления в большую сторону — 5-5-5-15. Второму значению (CL X-1 = 4) соответствует несколько устаревший режим DDR2-533 (время цикла 3.75 нс, частота 266.7 МГц) с нецелой схемой таймингов 4-3.33-3.33-9.87, которую с учетом округления можно записать в виде 4-4-4-10. Как мы уже отмечали выше, дважды уменьшенной величине задержки CAS# (CL X-2 = 3) не соответствует какой-либо осмысленный режим функционирования модулей, что определенно является ошибкой.

Идентификационный код производителя и Part Number модуля указаны верно, однако информация о дате изготовления и серийном номере модулей отсутствует. Данные модули также поддерживают расширения EPP, поэтому рассмотрим ниже информацию, содержащуюся в этой части SPD.

| Параметр | Байт(ы) (биты) | Значение | Расшифровка |

|---|---|---|---|

| Строка идентификации EPP | 99-101 | 4E566Dh | Есть поддержка SPD EPP |

| Тип профилей EPP | 102 | B1h | Расширенные профили |

| Профиль оптимальной производительности | 103 (1:0) | 01h | Профиль 1 |

| Используемые профили | 103 (7:4) | 03h | Профиль 0: присутствует Профиль 1: присутствует |

| Профиль №0 | |||

| Уровень питающего напряжения | 104 (6:0) | 14h | 2.3 V |

| Задержка передачи адреса (Addr CMD rate) | 104 (7) | 01h | 2T |

| Время цикла (tCK) | 109 | 22h | 2.20 нс (454.5 МГц) |

| Задержка CAS# (tCL) | 110 | 10h | 4 |

| Минимальная задержка между RAS# и CAS# (tRCD) | 111 | 23h | 8.75 нс (3.98) |

| Минимальное время подзарядки данных в строке (tRP) | 112 | 19h | 6.25 нс (2.84) |

| Минимальная длительность импульса сигнала RAS# (tRAS) | 113 | 21h | 33.0 нс (15.00) |

| Период восстановления после записи (tWR) | 114 | 28h | 10.0 нс (4.55) |

| Минимальное время цикла строки (tRC) | 115 | 32h | 50.0 нс (22.73) |

| Профиль №1 | |||

| Уровень питающего напряжения | 116 (6:0) | 14h | 2.3 V |

| Задержка передачи адреса (Addr CMD rate) | 117 (7) | 01h | 2T |

| Время цикла (tCK) | 121 | 22h | 2.20 нс (454.5 МГц) |

| Задержка CAS# (tCL) | 122 | 10h | 4 |

| Минимальная задержка между RAS# и CAS# (tRCD) | 123 | 21h | 8.25 нс (3.75) |

| Минимальное время подзарядки данных в строке (tRP) | 124 | 19h | 6.25 нс (2.84) |

| Минимальная длительность импульса сигнала RAS# (tRAS) | 125 | 1Fh | 31.00 нс (14.09) |

| Период восстановления после записи (tWR) | 126 | 30h | 12.00 нс (5.45) |

| Минимальное время цикла строки (tRC) | 127 | 2Ch | 44.00 нс (20.00) |

Содержимое EPP выглядит весьма интересным. В отличие от рассмотренных выше модулей OCZ DDR2 PC2-6400 с «сокращенными» профилями EPP, рассматриваемые модули OCZ DDR2 PC2-7200 содержат в своей части EPP информацию о двух «расширенных» профилях (№0 и №1), оба из которых являются действительными, но соответствуют... примерно одному и тому же режиму функционирования(!), не считая незначительных различий. А именно, в обоих профилях рабочим режимом модулей является режим «DDR2-900» (частота — примерно 454.5 МГц, время цикла 2.2 нс) с питающим напряжением 2.3 V (что соответствует спецификациям производителя) и величиной задержек командного интерфейса 2T. Несколько различаются лишь схемы основных таймингов памяти, которые в первом случае можно представить в виде 4-3.98-2.84-15 (4-4-3-15 при округлении в большую сторону), а во втором — как 4-3.75-2.84-14.09. При округлении этих значений также получается схема 4-4-3-15 (совпадающая с заявленной производителем), однако профили EPP также несколько различаются по значениям «прочих» таймингов вроде tWR и tRC. Как бы там ни было, «оптимальным» профилем выбран профиль №1.

Содержимое SPD рассматриваемых модулей OCZ DDR2 PC2-7200 (включая расширения EPP) явно отличается от содержимого SPD (и EPP) рассмотренных выше модулей OCZ DDR2 PC2-6400. Так или иначе, в обоих случаях наблюдаются неточности, а то и явные ошибки. Таким образом, подход компании OCZ к программированию данных SPD оказывается весьма своеобразным, если не сказать — весьма небрежным. Напоследок, рассмотрим содержимое SPD последнего представителя — модулей OCZ DDR2 PC2-8000, которое представлено лишь «стандартной» частью ввиду отсутствия поддержки расширений EPP.

OCZ DDR2 PC2-8000

| Параметр | Байт | Значение | Расшифровка |

|---|---|---|---|

| Фундаментальный тип памяти | 2 | 08h | DDR2 SDRAM |

| Общее количество адресных линий строки модуля | 3 | 0Eh | 14 (RA0-RA13) |

| Общее количество адресных линий столбца модуля | 4 | 0Ah | 10 (CA0-CA9) |

| Общее количество физических банков модуля памяти | 5 | 61h | 2 физических банка |

| Внешняя шина данных модуля памяти | 6 | 40h | 64 бит |

| Уровень питающего напряжения | 8 | 05h | SSTL 1.8V |

| Минимальная длительность периода синхросигнала (tCK) при максимальной задержке CAS# (CL X) | 9 | 25h | 2.50 нс (400.0 МГц) |

| Тип конфигурации модуля | 11 | 00h | Non-ECC |

| Тип и способ регенерации данных | 12 | 82h | 7.8125 мс — 0.5x сокращенная саморегенерация |

| Ширина внешнего интерфейса шины данных (тип организации) используемых микросхем памяти | 13 | 08h | x8 |

| Ширина внешнего интерфейса шины данных (тип организации) используемых микросхем памяти ECC-модуля | 14 | 00h | Не определено |

| Длительность передаваемых пакетов (BL) | 16 | 0Ch | BL = 4, 8 |

| Количество логических банков каждой микросхемы в модуле | 17 | 04h | 4 |

| Поддерживаемые длительности задержки CAS# (CL) | 18 | 38h | CL = 5, 4, 3 |

| Минимальная длительность периода синхросигнала (tCK) при уменьшенной задержке CAS# (CL X-1) | 23 | 30h | 3.00 нс (333.3 МГц) |

| Минимальная длительность периода синхросигнала (tCK) при уменьшенной задержке CAS# (CL X-2) | 25 | 37h | 3.70 нс (270.3 МГц) |

| Минимальное время подзарядки данных в строке (tRP) | 27 | 32h | 12.5 нс 5.00, CL = 5 4.17, CL = 4 3.37, CL = 3 |

| Минимальная задержка между активизацией соседних строк (tRRD) | 28 | 28h | 10.0 нс 4.00, CL = 5 3.33, CL = 4 2.70, CL = 3 |

| Минимальная задержка между RAS# и CAS# (tRCD) | 29 | 32h | 12.5 нс 5.00, CL = 5 4.17, CL = 4 3.37, CL = 3 |

| Минимальная длительность импульса сигнала RAS# (tRAS) | 30 | 25h | 37.0 нс 14.80, CL = 5 12.33, CL = 4 10.00, CL = 3 |

| Емкость одного физического банка модуля памяти | 31 | 80h | 512 МБ |

| Период восстановления после записи (tWR) | 36 | 3Ch | 15.0 нс 6.00, CL = 5 5.00, CL = 4 4.05, CL = 3 |

| Внутренняя задержка между командами WRITE и READ (tWTR) | 37 | 1Eh | 7.5 нс 3.00, CL = 5 2.50, CL = 4 2.02, CL = 3 |

| Внутренняя задержка между командами READ и PRECHARGE (tRTP) | 38 | 1Eh | 7.5 нс 3.00, CL = 5 2.50, CL = 4 2.02, CL = 3 |

| Минимальное время цикла строки (tRC) | 41, 40 | 36h, 00h | 54.0 нс 21.60, CL = 5 18.00, CL = 4 14.59, CL = 3 |

| Период между командами саморегенерации (tRFC) | 42, 40 | 69h, 00h | 105.0 нс 42.00, CL = 5 35.00, CL = 4 28.38, CL = 3 |

| Максимальная длительность периода синхросигнала (tCKmax) | 43 | 80h | 8.0 нс |

| Номер ревизии SPD | 62 | 12h | Ревизия 1.2 |

| Контрольная сумма байт 0-62 | 63 | DAh | 218 (верно) |

| Идентификационный код производителя по JEDEC | 64-71 | 7Fh, 7Fh, 7Fh, 7Fh, B0h | OCZ |

| Part Number модуля | 73-90 | — | OCZ2TA1000VX21G |

| Дата изготовления модуля | 93-94 | 00h, 00h | Не определено |

| Серийный номер модуля | 95-98 | 00h, 00h, 00h, 00h | Не определено |

Содержимое SPD этих модулей примерно совпадает с таковым для первого из изучаемых образцов — модулей OCZ DDR2 PC2-6400. Поддерживаемые значения задержки сигнала CAS# составляют 5, 4 и 3. Первому значению (CL X = 5) соответствует период синхросигнала 2.5 нс (частота 400 МГц), т.е. режим DDR2-800. Схема таймингов для этого случая записывается в виде 5-5-5-14.8 (5-5-5-15). Уменьшенной величине задержки CAS# (CL X-1 = 4) соответствует режим DDR2-667 (время цикла 3.0 нс, частота 333.3 МГц) со схемой таймингов 4-4.17-4.17-12.33 (4-5-5-13). Наконец, дважды уменьшенной величине задержки CAS# (CL X-2 = 3) соответствует несколько ошибочная, но распространенная запись режима DDR2-533 со временем цикла 3.7 нс (частота 270.3 МГц). Схема таймингов для этого случая — 3-3.37-3.37-10.0 (3-4-4-10).

Идентификационный код производителя и Part Number модуля указаны верно; данные о дате изготовления и серийном номере модуля отсутствует.

Конфигурация тестового стенда

Стенд №1

- Процессор: AMD Athlon 64 X2 4800+ (Socket AM2), номинальная частота 2.4 ГГц (200 x12)

- Чипсет: NVIDIA nForce 590 SLI

- Материнская плата: ASUS CROSSHAIR, версия BIOS 0502 от 01/02/2007

Результаты исследования

Испытание модулей OCZ проводилось на платформе AMD (процессор Athlon 64 X2 4800+) с материнской платой ASUS CROSSHAIR (стенд №1), поддерживающей стандарт EPP. Во всех случаях, испытания модулей проводились в двух режимах:

1. Номинальный: штатная частота процессора, частота памяти 400 МГц (DDR2-800), стандартная настройка подсистемы памяти по данным SPD, информация профилей EPP не используется.

2. Оптимальный, соответствующий использованию «оптимального» профиля EPP, допускающий разгон процессора (до 15%) для достижения максимальной рекомендованной частоты памяти. Для модулей OCZ DDR2 PC2-8000, не поддерживающих EPP, настройка частоты процессора и памяти в этом случае проводилась вручную.

OCZ DDR2 PC2-6400

| Параметр | Стенд №1 | |

|---|---|---|

| Частота процессора, МГц (частота FSB x FID) | 2400 (200x12) | 2400 (200x12) |

| Частота памяти, МГц (DDR2 МГц) | 400 (800) | 400 (800) |

| Тайминги памяти по умолчанию, напряжение | 5-5-5-15-2T, 1.8 V | 4-4-4-15-1T, 2.0 — 2.3 V |

| Минимальные тайминги памяти, напряжение | 4-4-3-2T, 2.2 V | — |

| Средняя ПСП на чтение (ГБ/с), 1 ядро | 3.94 (4.06) | — |

| Средняя ПСП на запись (ГБ/с), 1 ядро | 3.27 (3.10) | — |

| Макс. ПСП на чтение (ГБ/с), 1 ядро | 7.84 (7.99) | — |

| Макс. ПСП на запись (ГБ/с), 1 ядро | 6.94 (6.93) | — |

| Средняя ПСП на чтение (ГБ/с), 2 ядра | 6.65 (6.98) | — |

| Средняя ПСП на запись (ГБ/с), 2 ядра | 3.96 (4.05) | — |

| Макс. ПСП на чтение (ГБ/с), 2 ядра | 8.65 (9.33) | — |

| Макс. ПСП на запись (ГБ/с), 2 ядра | 6.46 (6.61) | — |

| Минимальная латентность псевдослучайного доступа (нс) | 28.1 (26.7) | — |

| Минимальная латентность случайного доступа* (нс) | 80.7 (78.4) | — |

*размер блока 32 МБ

Начнем с рассмотрения результатов тестирования модулей памяти OCZ DDR2 PC2-6400, для которых производителем заявлено функционирование в режиме DDR2-800 с таймингами 4-4-4-15 и, что самое важное, задержками командного интерфейса 1T. Стандартные тайминги для этих модулей, как видно из представленной выше таблицы, выставляемые BIOS материнской платы по умолчанию, составляют 5-5-5-15-2T, а их скоростные показатели находятся на уровне, типичном для DDR2-800 при данной частоте процессора (2.4 ГГц). Поднятие питающего напряжения до 2.2 V позволяет снизить схему таймингов до 4-4-3 (как и подавляющее большинство остальных модулей DDR2, рассматриваемые модули не чувствительны к изменению последнего стандартного параметра схемы таймингов tRAS), однако величина задержек командного интерфейса по-прежнему должна оставаться на уровне 2T. Попытки использования более жесткой схемы таймингов 4-3-3-2T, а также режима 1T при любых значениях таймингов приводили к возникновению ошибок подсистемы памяти.

Таким образом, рассматриваемые модули OCZ DDR2 PC2-6400, рассчитанные на функционирование в режиме DDR2-800 4-4-4-15-1T, оказались неспособны на работу в таком режиме. Не спасло положение и использование данных профиля EPP (не удивительно, ведь содержимое EPP в данных модулях представлено лишь одним «сокращенным» профилем, не позволяющим настроить дополнительные тонкие параметры временного и электрического характера), даже при попытке поднятия питающего напряжения вплоть до 2.3 V.

OCZ DDR2 PC2-7200

| Параметр | Стенд №1 | |

|---|---|---|

| Частота процессора, МГц (частота FSB x FID) | 2400 (200x12) | 2736 (228x12) |

| Частота памяти, МГц (DDR2 МГц) | 400 (800) | 456 (912) |

| Тайминги памяти по умолчанию, напряжение | 5-5-5-15-2T, 1.8 V | 4-4-3-15-2T, 2.2 V |

| Минимальные тайминги памяти, напряжение | 4-3-3-1T, 2.3 V | — |

| Средняя ПСП на чтение (ГБ/с), 1 ядро | 3.94 (4.12) | 4.56 |

| Средняя ПСП на запись (ГБ/с), 1 ядро | 3.30 (3.42) | 3.84 |

| Макс. ПСП на чтение (ГБ/с), 1 ядро | 7.83 (8.13) | 9.04 |

| Макс. ПСП на запись (ГБ/с), 1 ядро | 6.94 (6.79) | 7.88 |

| Средняя ПСП на чтение (ГБ/с), 2 ядра | 6.65 (7.14) | 7.79 |

| Средняя ПСП на запись (ГБ/с), 2 ядра | 3.93 (4.51) | 4.82 |

| Макс. ПСП на чтение (ГБ/с), 2 ядра | 8.69 (9.82) | 10.26 |

| Макс. ПСП на запись (ГБ/с), 2 ядра | 6.46 (6.69) | 7.52 |

| Минимальная латентность псевдослучайного доступа (нс) | 28.1 (25.7) | 23.9 |

| Минимальная латентность случайного доступа* (нс) | 80.2 (78.3) | 67.9 |

*размер блока 32 МБ

При запуске модулей OCZ DDR2 PC2-7200 в штатном режиме DDR2-800 принимающая участие в наших тестах материнская плата ASUS CROSSHAIR, как и в предыдущем случае, также выставляет схему таймингов 5-5-5-15-2T. Скоростные показатели модулей PC2-7200 в этом режиме близки к скоростным показателям модулей PC2-6400, рассмотренным выше. Наиболее интересно то, что при поднятии питающего напряжения модулей (до 2.3 V) они позволяют достичь схему таймингов 4-4-3 при величине задержек командного интерфейса 1T, чем резко отличаются от рассмотренных выше модулей PC2-6400, для которых режим 1T заявлен официально(!). Более того, в нашем случае оказалось возможным запустить рассматриваемые модули и при схеме таймингов 3-3-3-1T, однако это приводило к возникновению ошибок.

Применение «оптимального» профиля EPP привело к выставлению частоты «системной шины» процессора 228 МГц, что соответствует частоте шины памяти 228x2 = 456 МГц (режим «DDR2-912», несколько завышен по сравнению с номинальным «DDR2-900») при частоте процессора примерно 2.74 ГГц (для стабильности, напряжение на ядре процессора было вручную поднято до уровня 1.5 V). Применяемая схема таймингов при этом составила значения 4-4-3-15-2T, соответствующие с заявленными производителем. Рассматриваемые модули памяти оказались работоспособными в таком режиме, однако дальнейшее уменьшение таймингов (не считая игнорируемого параметра tRAS), а также снижение задержек командного интерфейса до 1T приводило к неработоспособности подсистемы памяти.

OCZ DDR2 PC2-8000

| Параметр | Стенд №1 | |

|---|---|---|

| Частота процессора, МГц (частота FSB x FID) | 2400 (200x12) | 2500 (250x10) |

| Частота памяти, МГц (DDR2 МГц) | 400 (800) | 500 (1000) |

| Тайминги памяти по умолчанию, напряжение | 5-5-5-15-2T, 1.8 V | 5-5-5-15-2T, 2.3 V |

| Минимальные тайминги памяти, напряжение | 4-3-3-1T, 2.3 V | 4-4-4-2T, 2.3 V |

| Средняя ПСП на чтение (ГБ/с), 1 ядро | 3.90 (4.13) | 4.35 (4.48) |

| Средняя ПСП на запись (ГБ/с), 1 ядро | 3.28 (3.33) | 3.61 (3.75) |

| Макс. ПСП на чтение (ГБ/с), 1 ядро | 7.79 (8.13) | 8.40 (8.50) |

| Макс. ПСП на запись (ГБ/с), 1 ядро | 6.94 (6.79) | 7.19 (7.21) |

| Средняя ПСП на чтение (ГБ/с), 2 ядра | 6.60 (7.14) | 7.52 (7.79) |

| Средняя ПСП на запись (ГБ/с), 2 ядра | 4.08 (4.46) | 4.70 (5.11) |

| Макс. ПСП на чтение (ГБ/с), 2 ядра | 8.61 (9.82) | 10.37 (11.01) |

| Макс. ПСП на запись (ГБ/с), 2 ядра | 6.48 (6.70) | 6.92 (7.04) |

| Минимальная латентность псевдослучайного доступа, нс | 28.6 (25.7) | 24.5 (23.2) |

| Минимальная латентность случайного доступа*, нс | 80.6 (78.4) | 72.1 (67.8) |

*размер блока 32 МБ

При эксплуатации последних из рассматриваемых нами модулей OCZ DDR2 PC2-8000 в официальном режиме DDR2-800 на материнской плате ASUS CROSSHAIR по умолчанию также выбирается схема таймингов 5-5-5-15-2T. Как и в случае модулей PC2-7200 (но не PC2-6400), увеличение питающего напряжения модулей до 2.3 V позволяет снизить эту схему до значений 4-3-3 (дальнейшее снижение до 3-3-3 приводит к возникновению ошибок), а величину задержек командного интерфейса — до 1T. Скоростные показатели модулей PC2-8000 и PC2-7200 в данном случае практически совпадают.

Поскольку модули OCZ DDR2 PC2-8000 не поддерживают расширения EPP, режим «DDR2-1000» был установлен вручную за счет увеличения частоты «системной шины» до 250 МГц для достижения частоты шины памяти 500 МГц при частоте процессора 2.5 ГГц (250x10). Минимальная схема таймингов, которую удалось достичь в этих условиях, составила 4-4-4-2T при питающем напряжении модулей 2.3 V, что совпадает со значениями, заявленными производителем (попытка выставления более низких значений практически моментально приводила к неработоспособности системы).

Итоги

Протестированные представители модулей памяти высокоскоростных серий от OCZ — PC2-6400, PC2-7200 и PC2-8000 произвели достаточно неоднозначные впечатления. Наименее приятные из них заключаются в достаточно небрежном подходе производителя к программированию содержимого SPD (в частности, расширений EPP), что может напрямую сказываться на совместимости модулей памяти с различными материнскими платами. Более того, первый из рассматриваемых представителей — модули памяти PC2-6400 — оказались неработоспособными в штатном режиме при величине задержек командного интерфейса 1T, официально заявленной производителем (по крайней мере, на используемой нами материнской плате ASUS CROSSHAIR). Из приятных моментов можно отметить работоспособность двух остальных представителей — модулей серии PC2-7200 SLI-Ready Edition и PC2-8000 Titanium Alpha VX2 в штатном режиме DDR2-800 при достаточно «экстремальной» схеме таймингов 4-3-3 и величине задержек командного интерфейса 1T, что далеко не типично для большинства 2-ГБ двухканальных комплектов модулей памяти на платформе AMD «AM2». В то же время, в «неофициальных» режимах («DDR2-900» и «DDR2-1000», соответственно) модули этих серий, по-видимому, оказываются разогнанными до предела, поскольку дальнейшее уменьшение схемы таймингов, а также снижение задержек командного интерфейса до 1T не представляется возможным. Однако само по себе устойчивое функционирование модулей PC2-7200 и PC2-8000 в максимально скоростных режимах, учитывая возникшую ситуацию с модулями PC2-6400, уже можно считать плюсом этих серий продукции компании OCZ.

Средняя текущая цена (количество предложений) в московской рознице:

| Модули памяти OCZ DDR2 PC2-6400 2 x 1ГБ (OCZ2T8002GK) | Н/Д(0) |

| Модули памяти OCZ DDR2 PC2-7200 2 x 1ГБ (OCZ2N900SR2GK) | Н/Д(0) |

| Модули памяти OCZ DDR2 PC2-8000 2 x 1ГБ (OCZ2TA1000VX22GK) | Н/Д(0) |