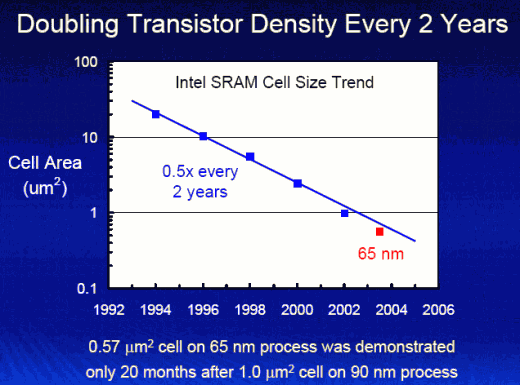

Итак, исторический факт, знаменующий выпуск первых чипов с нормами 65 нм техпроцесса, можно назвать свершившимся. Сегодня компания Intel представила первые полностью функциональные 4 Мбит чипы статической памяти SRAM (Static Random Access Memory), выполненные с этими нормами. Разумеется, до начала массового производства чипов с 65 нм нормами еще далеко — даже Intel планирует массовые поставки таких микросхем только в 2005 году, однако, уже сейчас можно констатировать факт: Земля по-прежнему вертится, закон Мура по-прежнему в силе.

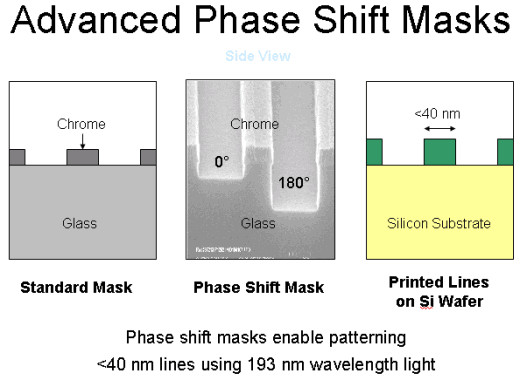

Двадцать месяцев назад компания Intel показала прототипы первых чипов SRAM, выполненные с нормами 90 нм техпроцесса. Тогда это событие было также первым в индустрии и представляло собой настоящий технологический прорыв. Сегодня мы говорим о внедрении 90 нм норм, практически, как о факте, если не свершившимся, то по крайней мере, реальном, появление таких чипов в ближайший год от многих производителей уже не вызывает удивления. Между тем, для того, чтобы получить на практике новые чипы с техпроцессом P1264, с 65 нм нормами, где ширина затвора транзистора не превышает 35 нм (для сравнения: затворы транзисторов процессора Intel Pentium 4 имеют порядка 50 нм), специалистам Intel вновь пришлось идти на многочисленные инженерные ухищрения. И дело не только во внедрении компанией второго поколения технологии так называемого «растянутого» (strained) кремния, медных соединений и использования новых low-k диэлектриков. Дело в том, что в очередной раз компания столкнулась с тем, что для производства чипов с новыми нормами пришлось использовать прежние инструменты вкупе с технологией фазового сдвига фотомасок. Наши постоянные читатели, возможно, помнят предшествовавший материал, описывавший сложности при переходе на 0,13 мкм техпроцесс, трудности с поставками новых 197 нм литографических инструментов и необходимость работы с прежними 248 нм литографическими инструментами (см. статью Перспективы нынешней литографии глазами Intel, или «Прощай, SVG!» от 2 августа 2001 года, а также тематически связанную с ней публикацию Intel покупает первую EUV-установку. Немного о перспективах внедрения EUV от 24 апреля 2002 года). На этот раз компания также использовала технологию фазового сдвига, однако, уже с поколением 193 нм сканеров. Впрочем, по всей видимости, сейчас — самое время поведать подробности о шагах, предваряющих появление на свет микросхемы. Сегодня мы вкратце коснемся процесса изготовления кремниевой пластины, чтобы впоследствии более предметно говорить о возникающих на пути разработчиков проблемах и методах их устранения.

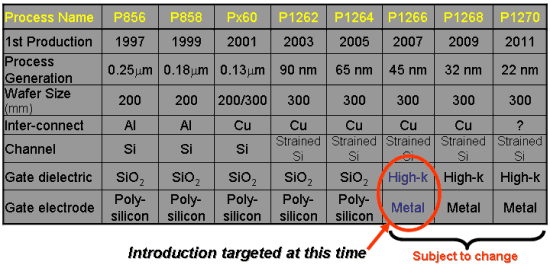

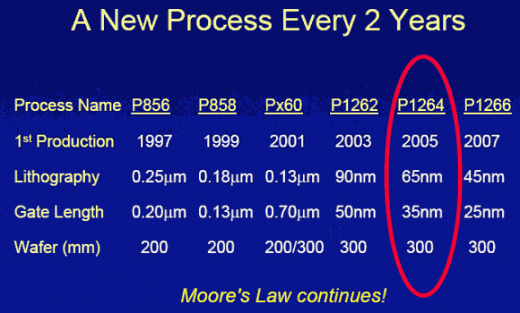

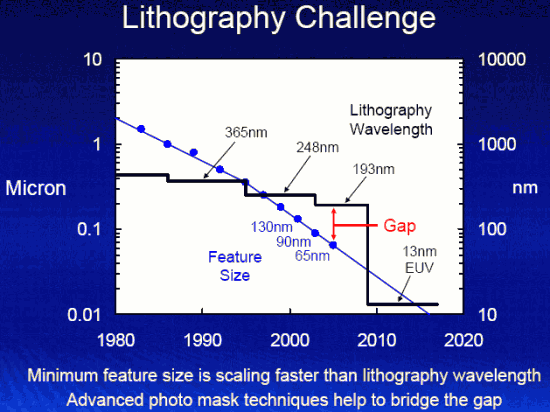

Итак, Intel самой первой столкнулась с проблемами перехода к 65 нм нормам. Посмотрим на планы развития технологических процессов Intel. Нынешний «литографический» роадмэп компании выглядит таким образом:

Как и в прошлый раз, два года назад, когда речь шла о форсировании внедрения в массовое производство норм 0,13 мкм техпроцесса, Intel вновь столкнулась с тем, что современное состояние индустрии производства инструментов для выпуска чипов пока не готово к поставкам желательных в этом случае новых литографических установок. Напомню, что летом 2001 года специалисты Intel, в очередной раз услышавшие от SVG об отсрочке начала поставок 193 нм литографических инструментов, смогли перейти с 0,18 мкм норм на 0,13 благодаря применению технологии сдвига фазы при экспонировании фотомасок с применением прежних 248 нм инструментов.

Прошло время, массовые поставки 193 нм степперов вошли в график, а это как раз «то, что доктор прописал» для производства 90 нм чипов. Однако уже опробованная технология сдвига фазы, доработанная с учетом требований норм 65 нм техпроцесса, позволила специалистам Intel сделать прошедшим летом сенсационное заявление: следующее поколение 157 нм литографических инструментов компанией будет попросту пропущено. То есть, ближе к 2009 — 2010 годам, когда подойдет срок внедрения 32 нм техпроцесса, Intel намерена перейти сразу с 193 нм инструментов на экспозиционные установки технологии сверхглубокого ультрафиолета (Extreme Ultraviolet, EUV). Вопрос этот, надо сказать, до сих пор остается открытым. Дело в том, что 157 нм литография, мало того, что до сих выпускается лишь в единичных опытных экземплярах, стоит к тому же, из-за высоких цен на CaF оптику, дурных денег — что-то порядка $40-50 млн. за установку. Справедливости ради стоит отметить, что не все производители полупроводников отказались от планов использования 157 нм оборудования, да и в Intel, в целом, не отрицают возможности «промежуточных» — до ввода EUV литографии, закупок таких инструментов или чего-нибудь альтернативного, вроде иммерсионной литографии.

Тем не менее, нынешняя ситуация привела к разработке технологии «печати» 65 нм чипов с помощью прежних 197 нм инструментов. Делается это следующим образом. Внимательно рассмотрим следующий слайд:

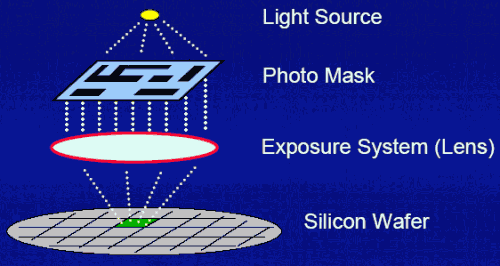

Как видите, схематично экспонирующая система выглядит очень просто: источник света (193 нм лазер) «засвечивает» через шаблон-маску и фокусирующую систему кремниевую пластину. Мы не будем сейчас углубляться в хитрости техпроцесса, в работу с фоторезистами и ненормальные цены на подобную оптику, выделим лишь суть: для достижения 65 нм норм такая система не очень пригодна — слишком «длинноволновым» оказывается излучение 193 нм источника света. На помощь в этом случае приходит техника формирования отпечатка с помощью фазосдвигающей маски и технологии оптической коррекции, как показано на следующем слайде:

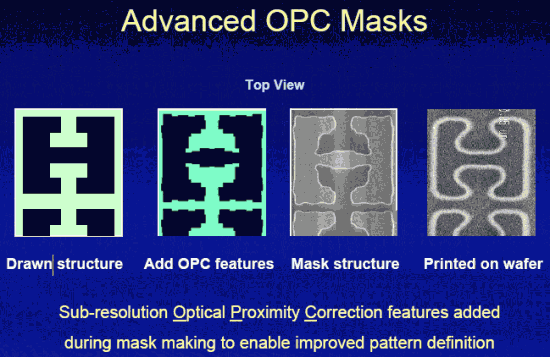

Таким образом, по уверениям специалистов компании, появляется возможность поддерживать технологический процесс с нормами менее 40 нм! Получается, что этого предостаточно не только для работы с 65 нм нормами, но также со следующим, 45 нм поколением техпроцесса, называемым в Intel P1266 и подготавливаемым к внедрению в 2007 году. Вот таким образом работает технология оптической коррекции, применяемая при работе с «фазосдвинутыми» фотошаблонами (alternating phase shift mask, APSM) на практике:

Итого, в результате получается достаточно оперативная и производительная работа с пластиной: представьте себе, что на работу с первыми тремя наиболее критичными слоями уходит всего пять дней! Несмотря на то, что пока что компания работает лишь с опытными образами 65 нм чипов, уже сейчас специалисты Intel утверждают: процент выхода готовых чипов при начале массового производства будет впечатляющим.

Что из себя представляет нынешнее опытное производство с 65 нм нормами? Для организации этого техпроцесса компания оборудовала на площади в 35 тыс. кв. футов, на своей крупнейшей фабрике D1D по выпуску 300 кремниевых пластин в Хиллсборо, Орегон, тестовую линию с 193 нм литографическими инструментами. Техпроцесс включает в себя использование «растянутого» (strained) кремния, 8 слоев металлизации, медные соединения, технологию применения low-k диэлектриков, получаемых путем сублимационного химического замещения (CVD, chemical vapor deposition), при этом, коэффициент диэлектрической проницаемости материала — k, менее 3.0.

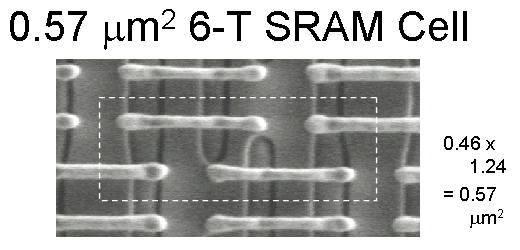

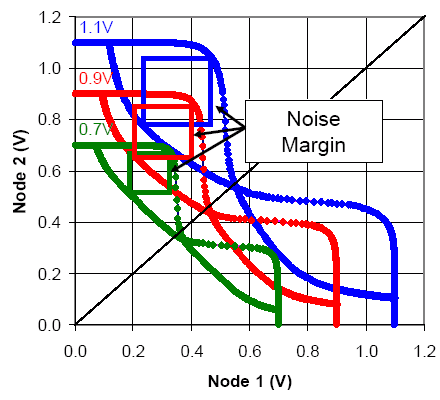

Представьте себе, что ячейка полнофункционального 4 Мбит чипа SRAM, выполненного с нормами 65 нм, занимает площадь всего 0,57 нм²! Для того, чтобы более предметно представить порядок этих габаритов, можно сказать, что на площади в один квадратный миллиметр размещается порядка 10 млн. таких транзисторов, а сама ячейка состоит из 6 транзисторов. Стоит также отметить, что малый форм-фактор экспериментальных чипов SRAM не является единственной целью разработчиков. Изменение норм техпроцесса приносит с собой совершенно иные, меньшие рабочие напряжения питания, и здесь очень важным является тот факт, что снижение питания чипов до 0,7 В оставило вполне приличный «зазор» по шумовым характеристикам.

Фабрика D1D, являющаяся уже четвертым предприятием Intel по производству 300 мм кремниевых пластин, будет одной из первых, которая перейдет на выпуск чипов с соблюдением норм 65 нм и 45 нм техпроцесса, при этом, речь идет не только о производстве памяти, но также следующих поколений процессоров Pentium. Что касается нынешних экспериментальных чипов, они также имеют отношение к CPU, так как именно SRAM является памятью, применяемой в качестве кэша процессора.

Вот, собственно, вкратце все, что можно рассказать о новом 65 нм техпроцессе, освоенном в опытном порядке компанией Intel. Есть все шансы, что мы увидим первые процессоры с применением 65 нм техпроцесса P1264 уже в 2005 году. Дальнейшие планы Intel по внедрению новых техпроцессов выглядят в настоящее время следующим образом: