В начале декабря в Монтерее, что находится в штате Калифорния, прошла конференция ACM/IEEE Tau workshop, посвященная, в частности, проблемам синхронизации различных чипов на высоких частотах. Открывая конференцию, Айвэн Сатерленд (Ivan E. Sutherland), вице-президент Sun Microsystems, определил дальнейший ход дискуссии: асинхронный дизайн чипов и вероятностный подход к проблеме синхронизации быстродействующих чипов. В ходе докладов многих участников оформилась и приобрела очертания любопытная идея: использовать для управления временем задержки прихода синхроимпульсов не детерминированный, а вероятностный подход. Многие сошлись во мнении, что вероятностный подход позволит более эффективно использовать разброс значений времени, в который импульс электрического тока приходит из одной части чипа в другой.

Итак, для корректной работы сложной логической схемы важно точно синхронизировать все логические элементы. Для большей наглядности изложения, нарисуем очень простую схему, изображающую последовательность логических элементов.

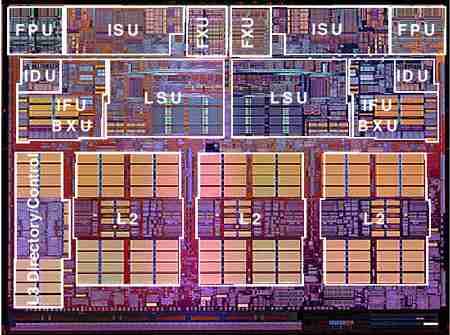

На низких частотах скорость распространения электрического импульса, предназначенного для синхронизации обоих логических элементов, много больше скорости срабатывания самого логического элемента, и это значит, что синхронизирующий импульс от задающего тактового генератора придет на вход синхронизации следующего логического элемента задолго до того, как на выходе логического элемента установится уровень логического нуля или единицы. Если же время распространения синхроимпульса по шине синхронизации сравнимо со временем срабатывания первого логического элемента, синхронизация второго логического элемента по-прежнему возможна, но уже потребуется учет времени задержки прихода синхронизирующего импульса. К счастью для пользователей и к сожалению для инженеров-проектировщиков, у которых прибавилось головной боли, нынешние быстродействующие чипы достигли той скорости работы, когда требуется аккуратно учитывать временные задержки прихода как синхронизирующих, так и сигнальных импульсов в различные части микросхемы. В принципе, зная путь, который должен пройти электрический сигнал, можно оценить эти задержки во времени, но помимо схематических особенностей, на время задержки оказывают влияние и такие факторы, как логическое состояние структурных единиц чипа и погрешности технологического процесса. Погрешности при изготовлении отдельно взятого чипа могут оказать настолько сильное влияние на его работу, что неудивительно, почему при внедрении новых технологических процессов промышленники так сильно сетуют на чрезвычайно низкий уровень выхода полезных чипов. Совокупность этих факторов приводит к необходимости рассмотрения времени задержки как случайной величины, уникальной для каждого чипа и описания ее средним значением и дисперсией.

Выступивший на конференции Курт Кейтцер (Kurt Keutzer), профессор Калифорнийского Университета в Беркли, считает, что наступил момент, когда разработчикам передовых технологий следует отойти от традиционного детерминистского подхода к разработке новых чипов и рассматривать их как стохастические вычислительные устройства. Похожего мнения придерживается и Чанду Висвесвария (Chandu Visweswariah), один из директоров научно-исследовательского центра Томаса Уотсона (Thomas J. Watson Research Center) компании IBM, считая, что эра детерминистских чипов прошла и наступает век вероятностного проектирования, анализа и тестирования чипов. По сути дела, считает Висвесвария, эта эра началась еще тогда, когда человечество достигло порога 0,18-мкм норм техпроцессов.

Впрочем, не все участники конференции поддержали стремление как можно скорее перейти к вероятностному подходу. Так, Ави Эфрати (Avi Efrati), разработчик архитектур для верификации производительности систем Intel, придерживается мнения, что точное измерение и настройка времен синхронизации все еще является ключевым моментом для разработки новых чипов, и что говорить о революции пока рановато. Тут, конечно, трудно возразить, тем более что Intel, бесспорно, преуспела в методах настройки времен синхронизации и может похвастаться самыми быстрыми процессорами. Но что же все-таки таится за словосочетанием «вероятностный подход»?

Преимущества вероятностного подхода

Существующий подход в разработке чипов использует измеренные постоянные номинальные времена задержек для разных частей микросхемы. Вариации этих времен определяют устойчивость работы чипа и обычно их стремятся сделать как можно меньшими, так как они только вредят. Стохастический же подход, хотя и кажется намного более сложным, может оказаться более продуктивным, так как случайные вариации можно обратить на пользу, и уж во всяком случае, их учет может стать более детальным, нежели просто как факторов, влияющих на дисперсию времени задержки.

Статистический подход оперирует случайными величинами, которые, как уже говорилось выше, описываются средним значением и дисперсией (если выражаться математически строго, первым и вторым моментом), позволяющей найти разброс значений для времен задержки. Но статистический подход содержит в себе достаточно мощный инструмент, заключающийся в использовании функции распределения случайной величины, что дает возможность оценить, к примеру, что 70% проектируемых чипов будет работать на частоте 200 МГц, и только 25% — частоте 225 МГц. Таким образом, статистический расчет времен задержки позволит оценить выход полезных чипов.

Чтобы получить функцию распределения, хотелось бы знать основные характеристики случайных процессов, формирующих величину времени задержки. Выше упоминалось про погрешности, привносимые технологическим процессом, однако, как сообщил Кейтцер, есть и фундаментальные особенности строения структур из полупроводника, оксидов и металлов, образующих логические элементы. Бывает и так, что случайное допирование нескольких частиц примеси на поверхность кристалла полупроводника приводит к значительному изменению времени задержки в критических для современных частот масштабах: доли наносекунд. Кроме того, для корректного расчета времен задержки внутри блока микросхем придется использовать функции корреляции случайных параметров между собой. И, наконец, надо учесть корреляцию и взаимное влияние электрических полей в расположенных друг рядом с другом блоков чипа.

Конечно же, разработчики полупроводниковых микросхем уже задумывались над этим вопросом. На конференции были представлены результаты исследований корреляции флуктуаций параметров полупроводниковых чипов и их зависимости от условий техпроцесса компании Cadence. Кроме того, различные работы по вероятностному моделированию представили Гентский Университет Бельгии и Университет штата Мичиган, проводивший свое исследование вместе с Motorola.

Стоит отметить также, что хотя статистический подход и кажется более сложным, в распоряжении разработчиков уже давно имеется мощный математический аппарат, разрабатывавшийся в течение полутораста лет. Кроме того, в аналоговых чипах вероятностный подход используется уже достаточно давно, и теперь, по мнению Висвесвария из IBM, наступила пора применить его и для цифровых логических схем. Висвесвария уверен, что хотя разработчики ASIC, скорее всего, не воспримут идею усложнения расчетов с большим энтузиазмом, однако наверняка не преминут воспользоваться преимуществом оценки кривой выхода полезных чипов и, самое главное, смогут уменьшить время, требующееся для тестирования чипов.

I would like to give special thanks to Dr. Chandu Wisweswariah from IBM Thomas J. Watson Research Center for providing charts and graphs on timing issues presented at ACM/IEEE Tau workshop.