К7 — первый из семейства микропроцессоров х86 7-го поколения, в котором присутствуют конструктивные решения, до сих пор не применявшиеся в процессорах архитектуры х86 и сулящие выигрыш в быстродействии даже при одинаковых тактовых частотах. Наиболее впечатляющим из них является, конечно, 200-мегагерцовая системная шина, однако есть и другие, менее заметные на первый взгляд новшества, ставящие К7 выше процессоров 6-го поколения.

- Новая архитектура узла вычислений с плавающей точкой (fpu). К7 содержит 3 узла вычислений с плавающей точкой (fpu), любой из которых способен принимать на вход инструкции каждый такт работы процессора. При этом один узел предназначен исключительно для выполнения команды FSTORE! Назначение этого узла — обеспечивать обмен между регистрами и памятью в то время, как процессор выполняет другие инструкции. Такой подход, хотя и не повышает пиковую производительность, позволяет достичь более высокой средней производительности, что во многих случаях важнее. Остальные два fpu состоят из блока сложения (adder) и блока умножения (multiplier). Оба блока используют конвейеры (fully pipelined). Архитектура каждого fpu такова, что он может принимать на вход каждый такт одну инструкцию сложения и одну умножения, что дает пиковую производительность 1000MFLOPS при 500МГц. Ближайшим аналогом с точки зрения архитектуры является Pentium II, у которого также присутствуют adder и multiplier. Однако существуют два основных отличия. Во-первых, у PII только adder является полностью конвейеризованным (fully pipelined), multiplier же может принимать инструкцию на вход только каждый второй такт. Во-вторых, каждый узел fpu PII может принимать только одну инструкцию за такт, таким образом, пиковая производительность составляет 500MFLOPS при 500МГц. Вышесказанное ни в коем случае не является нападками на достойную архитектуру семейства Р6, которое до сих пор остается единственным семейством процессоров с конвейерным fpu. Да, чуть не забыл... Rise mP6, возможно, будет иметь архитектуру fpu, похожую на ту, что используется в К7 (как во всем, что связано с компанией Rise, здесь полно тумана, но компания уверенно заявляет, что fpu их процессора способен выполнять 2 инструкции х87 за такт), однако максимальная тактовая частота в 200МГц не позволяет этому процессору претендовать на место не только в "высшем обществе", но даже и в "среднем классе", поэтому сравнивать mP6 с К7 некорректно.

- Огромный кэш L1. Если помните, Pentium MMX-166 показывал такую же производительность на приложениях, не использующих инструкции ММХ, как и классический Pentium-200. В чем причина? А причина в том, что чип ММХ имел в 2 раза больше кэша L1 (32К против 16К). Это также объясняет, почему К6-200 приблизительно равен по производительности Pentium MMX-233 — он имеет 64К кэша. К чему это я? К тому, что в К7 кэш L1 увеличился еще в 2 раза — до 128К. Это еще не гарантирует эффективного роста производительности процессора с увеличением тактовой частоты, но, по крайней мере, устраняет опасность простоя, из-за обмена с памятью.

- Модернизируемый кэш L2. У К7 кэш L2 будет размещен, по примеру PII, в картридже, а не интегрирован в кристалл, как у К6-3. Результатом этого является возможность "модернизации" кэша. Первоначально его частота будет составлять 1/3 частоты процессора. В дальнейшем планируется выпуск версий с кэшем L2, работающим на частоте процессора, и, возможно, на половинной частоте. То же и с размером. К7 может нести кэш L2 размером от 512К в "нижних" моделях до 8МВ в серверных моделях "high-end" (впечатляюще, Xeon на сегодня имеет до 2МВ, но цена...).

Чипсеты

В своем ноябрьском пресс-релизе AMD объявила, что VIA Technologies — компания, приложившая большие усилия для популяризации стандарта Super7 — согласилась разработать чипсет под К7. Позднее прошла информация о том, что VIA представит сэмплы этого чипсета в первом квартале текущего года. Этот чипсет будет доступен приблизительно в то же время, что и К7. Также было заявлено, что VIA заинтересована в поддержке процессоров Alpha. В том же пресс-релизе названа еще одна компания, разрабатывающая чипсет под К7 — Acer Labs.

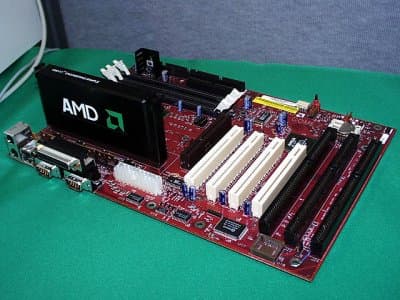

AMD разрабатывает и собственный недорогой чипсет под К7. Он состоит из северного моста (Northbridge) Irongate и южного моста (Southbridge) Cobra. На Comdex'98 демо-сэмпл К7 работал на системной плате с подозрительным названием Gomez.

Системные платы

Итак, плавно перешли к системным платам. Сразу после Comdex ходили упорные слухи, что компания ASUS рискнула делать платы со Slot-A. Хотя подтверждения этому до сих пор нет, такое развитие событий кажется вполне вероятным, особенно учитывая выход ASUS на рынок плат Super7.

FIC является близким партнером VIA (и, я думаю, владеет неплохим пакетом ее акций) и по этой причине, вероятно, станет одним из участников гонки производителей плат Slot-A. Опять-таки надо отметить большие успехи FIC на практически захваченном AMD рынке Super7, что даже позволяет компании объявить свою плату VA-503+ "самой популярной платой Super7".

Существенным является и тот факт, что платы Slot-A не содержат революционных новшеств и состоят из тех же физических частей, что и платы Slot-1. Они лишь электрически несовместимы. Таким образом, производителям не придется существенно перестраивать производство.

Планы

К7 и К6-3 планируется выпускать параллельно. Хотя практически все согласны с тем, что К7 будет наиболее мощной архитектурой, доступной в 1999 году, лишь немногие отдают себе отчет в том, что К7 уже не будет продуктом "на 25% дешевле Pentium II". Фактором, определяющим дешевизну К6-2 по сравнению с PII, является более низкая стоимость производства из-за меньшей площади кристалла (70 мм2 против 130 мм2 у Celeron). К7, изготовленный по 0.25-микронной технологии, будет иметь площадь кристалла 184 мм2, что превосходит параметры процессоров Intel. По этой причине где-то в течении полугода К7 будет дорогим продуктом, предназначенным для использования в серверах, high-end рабочих станциях и компьютерах наиболее продвинутых геймеров. Объемы производства будут невелики вплоть до перехода на 0.18-микронную технологию. Тогда размер кристалла К7 станет меньше 100 мм2, что сравнимо с параметрами Katmai/Coppermine, и К7 станет доступен для покупателей "верхнего среднего" сегмента рынка. В первые месяцы производства К7, его предшественник, К6-3, будет "прикрывать" средний сегмент рынка и напрямую конкурировать, по мнению AMD, с Katmai (К6-2 в это время, может быть, все еще будет конкурировать с Celeron). Одновременно с К7 на 0.18-микронную технологию переведут и производство К6-3. На этом этапе планируется прекратить производство К6-2, а К6-3 позиционируется как конкурент Интеловскому Coppermine.

В момент появления на рынке К7 будет иметь тактовую частоту 600МГц. Как AMD собирается этого достичь? Во-первых, как было сказано выше, процессор имеет суперконвейерную (superpipelined) архитектуру, специально оптимизированную для работы на высоких тактовых частотах, в отличие от ядра К6, которое уже порядком устарело и вред ли способно работать на частотах, превышающих 500МГц (по крайней мере, до перехода на 0.18-микронную технологию). Во-вторых, этот первый К7 будет иметь 128К кэша L1 (для сравнения: WinChip-3 — 128K L1, K6-3, Katmai, и Jedi — 64K L1) и 512К кэша L2, работающего на 1/3 частоты процессора. Очевидно, компания не уверена в том, что частоты кэша в 300МГц будет достаточно, и нашла изящный выход из положения — кэш L2, не мудрствуя, работает на частоте шины, а возможные узкие места устраняются путем увеличения размера кэша L1. Интересно, что 200-мегагерцовая шина, являющаяся одним из ключевых преимуществ K7, способна работать с обычной памятью SDRAM РС100, используя два банка памяти для работы на 200МГц. (Возможно, это и не так. Один представитель AMD говорил что-то о передаче данных как на возрастающем, так и на убывающем фронтах тактового сигнала).

Дешеветь К7 начнет в начале 2000 года (или в конце 1999, если все пойдет удачно с переходом на 0.18-микронную технологию). Необходимо, правда, учитывать, что и дешевый К7 будет стоить немногим больше $300.

Поводы для беспокойства

Во-первых, размер кэша L1. Некоторые специалисты отмечают, что кэш размера 128К может работать медленнее, чем обычный кэш (то есть, может иметь большее время доступа). Это может снизить максимальную производительность процессора, но он все равно будет работать быстрее аналогичного с кэшем 64К.

Во-вторых, частота кэша L2. Кэш 450-мегагерцового PII работает на большей частоте, чем 600-мегагерцового К7. Возможно, что большой размер кэша L2 решает эту проблему, однако он может стать проблемой сам по себе. Более того, совершенствование технологии и уменьшение времени доступа к кэшу представляют собой резерв повышения производительности К7. Серьезней другое. Из-за большого размера кэша кристалл К7 огромен. Это означает, в частности, что из пластины можно сделать меньше чипов. Из чего, в свою очередь, следует, что AMD сможет изготовить меньше процессоров и стоимость их производства будет выше. Такое положение дел может стать ключевым фактором, обеспечивающим выживание архитектуры Super7 после 2000 года. AMD вынуждена будет продолжать производить дешевую альтернативу дорогому К7!

Что день грядущий нам готовит?

Спецификация шины EV6 предусматривает частоту до 400МГц, так что с производством К7, работающего на 400-мегагерцовой шине, особых проблем не возникнет.

К7 может нести в картридже до 8МВ кэша L2, работающего на частоте процессора, что важно для серверов, и особенно для мультипроцессорных конфигураций SMP. Учитывая поддержку point-to-point SMP, К7, как утверждается, будет более эффективен в системах с большим числом процессоров, чем решения на базе Slot1. С переходом на 0.18-микронную технологию станет возможным интегрирование кэша L2, однако, учитывая и без того большую площадь кристалла, это решение вряд ли оправданно.

| Операции с плавающей точкой | K7 | K6-2 | K6-3 | Celeron-A | Pentium II | Pentium III |

|---|---|---|---|---|---|---|

| Avg. FPU latency Среднее число тактов на выполнение операции | 4 | 2 | 2 | 4 | 4 | 4 |

| x87 FMUL throughput (per issue) Тактов на выполнение конвейеризованной операции (на узел) | 1 | 2 | 2 | 2 | 2 | 2 |

| x87 FADD throughput (per issue) Тактов на выполнение конвейеризованной операции (на узел | 1 | 2 | 2 | 1 | 1 | 1 |

| # of issues per cpu clock cycle Число блоков, работающих каждый такт | 3 | 1 | 1 | 1 | 1 | 1 |

| Optimal x87 math ops per cycle Оптимальное число инструкций с плавающей точкой на такт | 2 | 1/2 | 1/2 | 1 | 1 | 1 |

| Память | K7 | K6-2 | K6-3 | Celeron-A | Pentium II | Pentium III |

|---|---|---|---|---|---|---|

| L1 cache size Размер кэша L1 | 128К | 64К | 64К | 32К | 32К | 64К? |

| L2 cache size Размер кэша L2 | 512K+ | - | 256K | 128K | 512K | 512K |

| L2 cache speed Частота кэша L2 | 1/3 | - | Full | Full | Half | Half |

| L3 cache size Размер кэша L3 | - | 512K-2M | 512K-2M | - | - | - |

| Memory bus speed Частота шины памяти | 200MHz+ | 95MHz, 100MHz | 100MHz | 66MHz | 100MHz | 100MHz, 133MHz |