Часть 2: новые процессоры, новые технологии

Не прошло недели с момента публикации предыдущего материала на тему технологий управления энергопотреблением современных процессоров, как в распоряжении нашей тестовой лаборатории оказался процессор Intel Pentium 4, а неделей позже — Intel Xeon с новой ревизией ядер Prescott и Nocona, соответственно (степпинг E0, сигнатура CPUID = 0F41h). Первый демонстрировал, на первый взгляд, весьма интересное поведение при нахождении в режиме простоя (о котором пойдет речь ниже). Причина этого явления была выяснена довольно скоро — оказалось, что новая ревизия ядра Prescott наряду с технологиями Execute Disable (XD bit) и Thermal Monitor 2 (TM2) поддерживает новую технологию «улучшенного режима простоя» (Enhanced Halt State, известную также как C1E). Аналогичный режим работы, наряду с серверной технологией Enhanced SpeedStep (DBS), реализован и в новой ревизии ядра Nocona. Настоящая статья посвящена изучению технологии C1E, а также механизма термального мониторинга №2, реализованного в процессорах Pentium 4/Xeon с выходом новой ревизии ядер Prescott/Nocona.

Конфигурация тестовых стендов

Стенд №1

- Процессор: Intel Pentium 4 3,6 ГГц (ядро Prescott, CPUID 0F41h)

- Чипсет: Intel 925XE

- Материнская плата: Intel D925XECV2, версия BIOS 1817 от 10/12/2004

- Память: 2x256 МБ Samsung DDR2-533

- Видео: Leadtek PX350 TDH, NVIDIA PCX5900

- HDD: WD Raptor WD360, SATA, 10000 rpm, 36GB

Стенд №2

- Процессоры: 2x Intel Xeon 3,6 ГГц (ядро Nocona, CPUID 0F41h)

- Чипсет: Intel E7520

- Материнская плата: Intel Server Board SE7250AF2, версия BIOS 2023 от 08/05/2004

- Память: 4x1024 МБ Patriot Registered DDR2-533

- Видео: ATI RAGE XL PCI (интегрированное)

- HDD: WD Raptor WD360, SATA, 10000 rpm, 36GB

Программное обеспечение

- RightMark CPU Clock Utility (RMClock) версии 1.3beta2

- Intel Desktop Utilities (Light) версии 2.0.11.46

- Intel Processor Identification Utility версии 1.01

- ThrottleWatch

Технология «улучшенного режима простоя» (Enhanced Halt State)

Согласно имеющейся документации, «улучшенный режим простоя» (C1E) представляет собой режим работы физического процессора с низким энергопотреблением, вхождение в который осуществляется при «усыплении» обоих логических процессоров (посредством выполнения инструкций HLT или MWAIT) при задействовании данной технологии со стороны BIOS. В чем же отличие данного режима пониженного энергопотребления от «обычного» Halt State (C1)? А в том, что в этом случае процессор способен динамически понижать коэффициент умножения частоты системной шины (FID) и уровень питающего напряжения (VID), и восстанавливаться до состояния максимальной производительности (номинальных FID/VID) по мере необходимости, причем — совершенно автоматически (без вмешательства со стороны операционной системы). Можно сказать, C1E представляет собой нечто среднее между довольно старой технологией ODCM, которая, как мы показали, автоматически снижает эффективную частоту процессора посредством ее модуляции в режиме простоя, и новой серверной технологией Enhanced SpeedStep (DBS), способной изменять эффективную частоту и питающее напряжение процессора, но не автоматически, а «по запросу».

Что ж, теперь самое время увидеть новую технологию в действии. Для этого используем нашу утилиту RMClock, которая с момента выхода предыдущей публикации уже успела «обрасти» дополнительными возможностями — в частности, специфических настроек функций управления энергопотреблением процессоров Intel Pentium 4, Xeon и Pentium M, позволяющими нам отныне обойтись без вспомогательных утилит вроде CPUMSR.

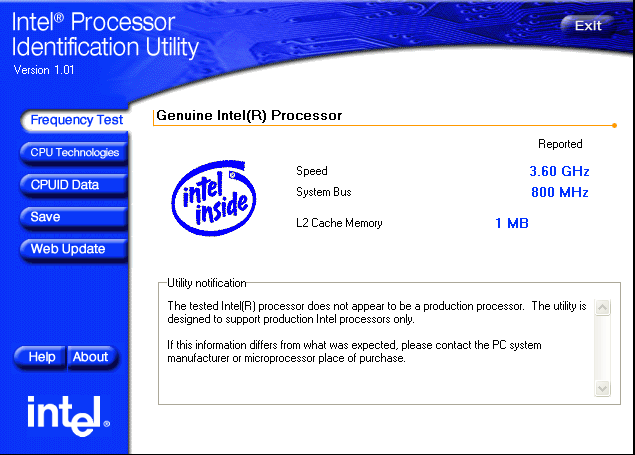

Прежде чем переходить к обсуждению результатов, нам следует сделать одну важную оговорку — поступивший в наше распоряжение процессор оказался инженерным образцом (как сообщает Intel Processor ID Utility). В связи с чем вполне можно ожидать, что поведение серийных образцов может отличаться от наблюдаемого в нашем сегодняшнем тестировании.

Второй важный момент — определение наличия технологии C1E пока что реализовано исключительно «методом тыка», в связи с чем носит предположительный характер (тем не менее, его функциональность проверена на практике).

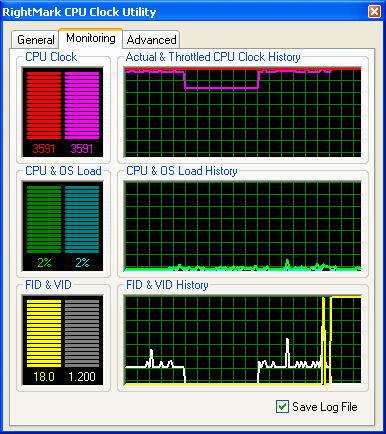

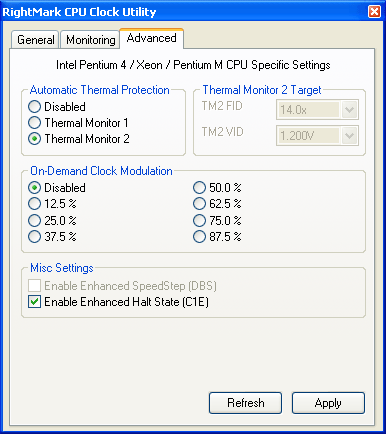

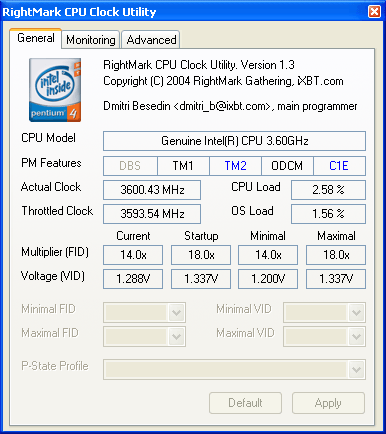

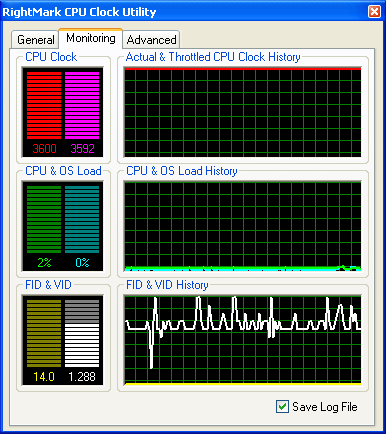

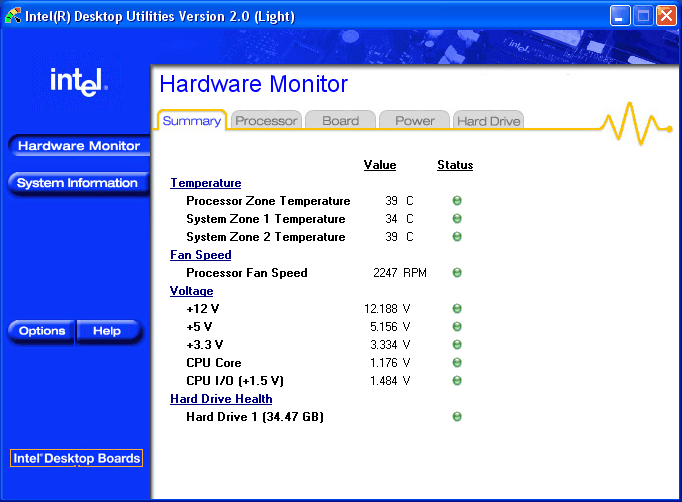

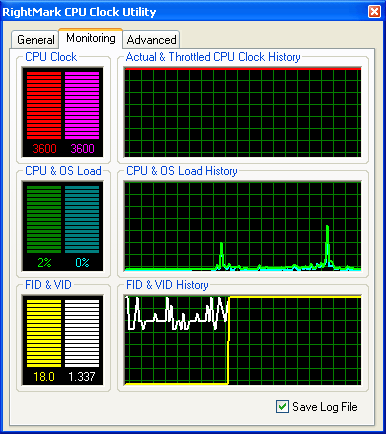

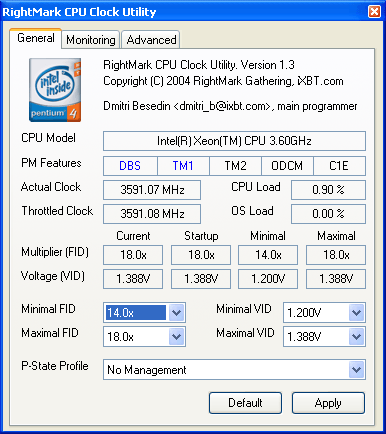

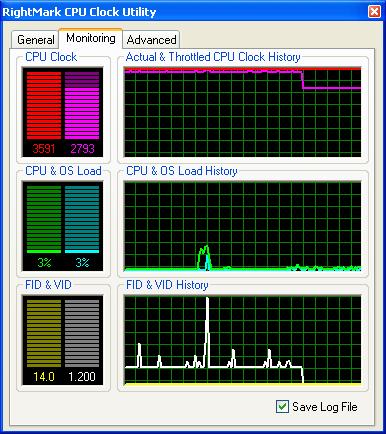

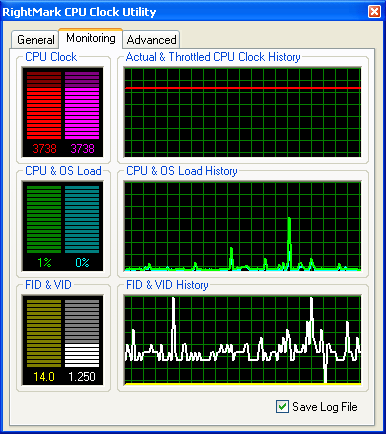

Переходим к главным закладкам приложения — так они выглядят после нескольких минут работы приложения в отсутствие загрузки процессора. По левой картинке видно, что процессор поддерживает технологии TM1, TM2, ODCM и C1E, из которых в данный момент (т.е. по умолчанию) задействованы только TM2 и C1E. Действие последней заметно уже здесь — для этого достаточно сравнить текущие значения FID и VID процессора с номинальными. Первое находится на минимальном уровне, второе — где-то посередине между минимумом и максимумом. Динамика изменений FID/VID отчетливо видна на правой картинке — при минимальной нагрузке на процессор FID остается на постоянно низком уровне (14x), VID колеблется в довольно широких пределах, а его средняя величина составляет примерно 60% от номинальной. Отметим, что изменения VID, вообще говоря, могут и не отражать реальные изменения питающего напряжения процессора, поскольку VID — это всего лишь значение напряжения, которое процессор запрашивает для собственного питания, а материнская плата в принципе вольна сделать с этим запросом все, что угодно (прежде всего, вообще ничего не менять). Тем не менее, в наших тестах изменение реального напряжения процессора также фиксировалось (с помощью утилиты Hardware Monitor из набора Intel Desktop Utilities, которая опирается на показания сенсоров материнской платы), причем последнее было занижено примерно на 0.1V относительно значений VID.

Итак, с FID и VID все замечательно, однако мы не можем пройти мимо одной очень важной детали — частоты процессора как таковой. Последняя, как «подлинная», измеренная по TSC, так и «эффективная» («частота троттлинга») как бы остается на… постоянно высоком уровне. Точнее, «частота троттлинга» попадает в область 3590…3600 МГц, что всего на 10 МГц ниже номинальной частоты. Ничего удивительно в этом, необычном на первый взгляд явлении, на самом деле нет. Учитывая саму природу технологии C1E (она активизируется только при вхождении обоих логических процессоров в состояние C1/HALT), не существует никакой возможности увидеть ее в действии. Ибо даже самые точные методы измерения частоты процессора в момент измерения неизбежно потребуют осуществить переход процессора из «спящего» состояния C1 в «рабочее» состояние C0, при котором восстанавливается его полная частота.

Ради интереса, попробуем отключить технологию C1E с помощью закладки настроек процессора.

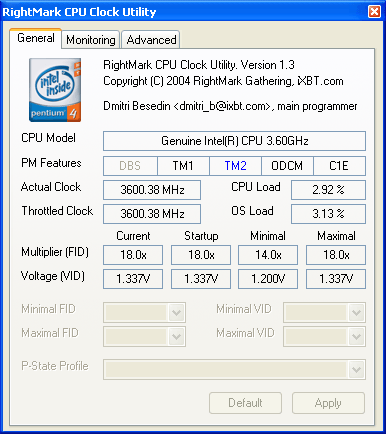

Результат весьма показательный — отключение C1E моментально сопровождается выставлением максимальных значений FID и VID в качестве текущих, после чего они остаются на постоянном уровне, независимо от загрузки процессора. А «эффективная частота» процессора стабилизируется на уровне, соответствующем его «истинной» (номинальной) частоте — 3600 МГц.

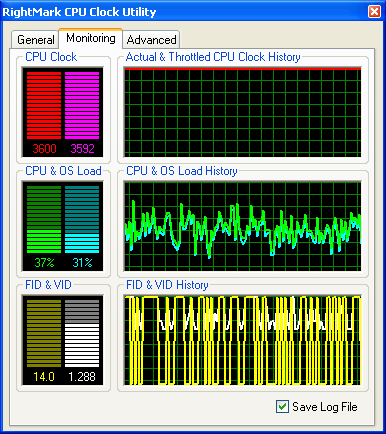

Следующий эксперимент — восстанавливаем функциональность C1E и подаем на процессор переменную нагрузку, имитируемую простым модельным приложением.

Кривые FID/VID убедительно показывают, что процессор способен быстро переключаться между состояниями минимальной и максимальной производительности. При этом количество состояний FID, судя по всему, всего два (начальное и конечное), тогда как изменения VID могут происходить через множество промежуточных состояний (с шагом в 0.0125В).

Таким образом, технология «усовершенствованного режима простоя» — весьма перспективное нововведение, призванное значительно снизить потребляемый процессором ток в режиме простоя в гораздо большей степени по сравнению с обычным режимом C1 (HALT). В связи с введением этой технологии может вполне закономерно возникнуть вопрос: если есть полностью автоматическая C1E (которой, кстати, оснащены и новые процессоры Xeon Nocona), зачем нужен Enhanced SpeedStep для серверов (DBS), требующий «ручного» (программного) управления? Ответ на этот вопрос весьма прост: C1E — действительно полностью автоматическая технология, она способна снижать энергопотребление процессора только при полном бездействии системы и моментально восстанавливать полную производительность при малейшей загрузке процессора, в то время как DBS может принудительно снижать потребляемую процессором мощность в условиях штатной работы, в т.ч. при значительной загрузке системы (если управляющее ПО «решит», что полная мощность сервера в данный момент не требуется).

Технология автоматического термального мониторинга №2

Внимательный читатель обязательно заметит: технология Thermal Monitor 2 уже обсуждалась в предыдущей статье, так зачем же снова уделять ей внимание? Ответ на сей вопрос будет достаточно простым и неожиданным — уже после тестирования обнаружилось, что исследованная модель Xeon Nocona (степпинг D0, сигнатура CPUID — 0F34h), оказывается, на самом деле… не поддерживает технологию TM2! Точнее, сказано так: «TM2 is enabled, but NOT supported». И ведь действительно Enabled — в CPUID Feature Flags указано наличие этой технологии. Да еще и прекрасно работает, как показывают тесты. Но, в то же время, «не поддерживается»… Вот мы и решили исследовать эту технологию на том процессоре (пусть и не серийном образце), который ее официально поддерживает.

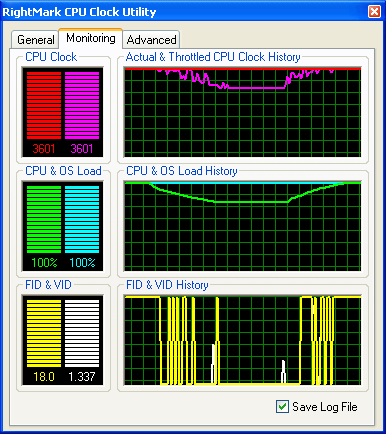

Методика ее исследования будет точно такой же: подаем 100% нагрузку на оба логических процессора, после чего останавливаем вентилятор на кулере процессора.

Результат выглядит вполне ожидаемо (а картина аналогична той, которую мы получили на процессоре Xeon) — по достижении процессором температуры 73°C наблюдается снижение «эффективной» частоты процессора наряду с плавным снижением его загрузки. По графику FID/VID видно колебание FID между двумя уровнями — минимальным и максимальным. В то же время заметно, что переключение VID может осуществляться через промежуточные состояния (как и в технологии C1E, только изменения происходят гораздо резче).

Примерно через минуту после остановки вентилятора технология TM2 начинает работать на полную мощность, при этом достигается «эффективная частота» процессора 2.8 ГГц, загрузка стабилизируется на уровне 77.7%, а FID/VID — на уровне целевых значений (TM2 Target FID/VID) 14x и 1.2V, соответственно.

Возобновление активного охлаждения процессора сопровождается рассмотренными выше изменениями, протекающими в обратном порядке.

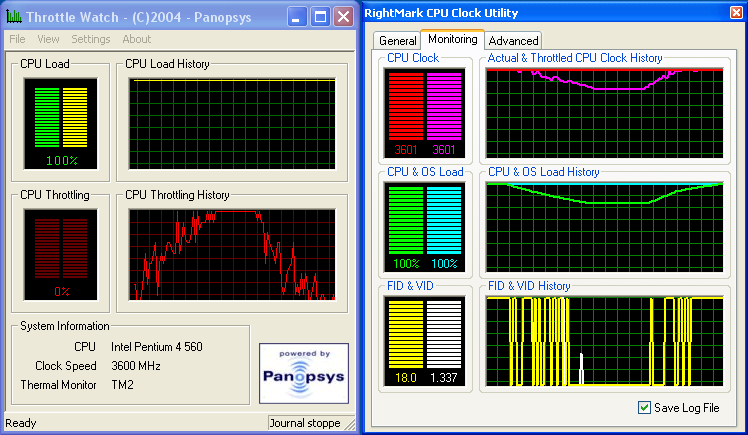

Для полноты картины, мы повторили данный тест, предварительно запустив утилиту стороннего производителя ThrottleWatch (учитывая, что на момент ее выпуска у нас уже не было возможности исследовать ее поведение при срабатывании TM2). Результат очевидный — ThrottleWatch способна как обнаружить, так и отследить момент срабатывания/выхода из режима TM2, однако ее функциональность в других режимах «троттлинга» процессора по-прежнему остается под вопросом.

Новая ревизия ядра Nocona процессоров Intel Xeon

Напоследок, рассмотрим аналогичную ревизию E0 (CPUID = 0F41h) ядра Nocona процессоров Intel Xeon 3.6 ГГц. Для начала, изучим, какие из рассматриваемых технологий управления энергопотреблением присутствуют и задействованы по умолчанию в этой категории процессоров.

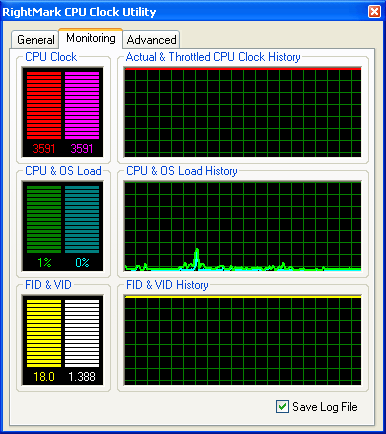

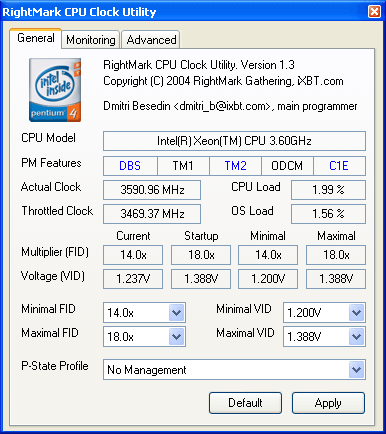

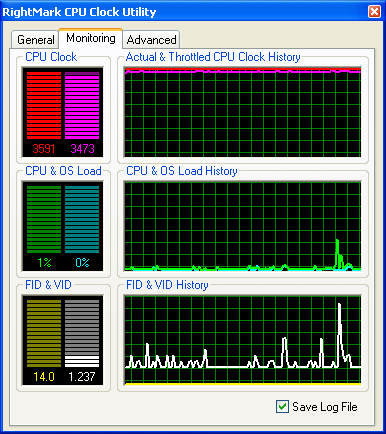

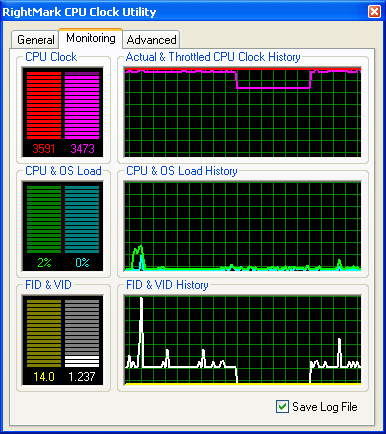

Итак, новая ревизия ядра Nocona поддерживает все пять «термальных» технологий — от «древних» ODCM и TM1 до новых и новейших TM2, DBS и C1E. Из них на момент запуска приложения включены DBS (кстати, заметим, что поддержку технологии серверного Enhanced SpeedStep можно включить/выключить в настройках BIOS; кроме того, она автоматически включается утилитой RMClock при ее запуске) и, как это ни странно, старый вариант термического троттлинга — механизм автоматического термального мониторинга №1 (TM1), в противоположность 3.6-ГГц процессору Pentium 4. Что интересно, настройки целевых значений FID/VID для TM2 выставлены BIOS-ом корректно (это можно увидеть по Minimal FID/VID), однако сама технология почему-то не включена по умолчанию. Наконец, заметим, что C1E по умолчанию также отключена (напомним, ее включение/выключение — также задача BIOS), что отчетливо видно по правому скриншоту: значения FID/VID не меняются с течением времени. Можно предположить, что «невключение» C1E на серверной платформе продиктовано соображениями максимальной производительности (минимального времени отклика сервера на запрос): из общих соображений очевидно, что как вход в состояние C1E, так и выход из него сопровождаются большими задержками по сравнению со входом в/выходом из обычного состояния C1 (HALT), в связи с необходимостью переключения режимов работы процессора (FID/VID) в сторону меньшего энергопотребления и обратно.

Как бы там ни поступал производитель процессоров, чипсетов и материнских плат со своей продукцией, нам ничего не мешает включить интересующие нас настройки вручную, с помощью закладки специфических настроек процессора (Advanced) утилиты RMClock. Включаем TM2 (его, в принципе, можно и не включать), C1E и смотрим на результат.

C1E в действии. «Коэффициент умножения» процессора упал до минимума — 14x (т.е., согласно нашей рабочей гипотезе, включилась модуляция частоты с циклом полезного действия процессора 77.7%), напряжение ядра начало «прыгать» между минимумом и максимумом, находясь большую часть времени на уровне 1.237V. Эффективная частота процессора снизилась, ее минимальный уровень находится вблизи 3470 МГц. Итак, технология C1E функционирует в процессорах Xeon (Nocona) корректно.

Посмотрим теперь, как сочетаются две новейшие функции управления режимами работы процессора — серверный Enhanced SpeedStep (DBS) и Enhanced Halt State (C1E) между собой, тем более что такую картину мы можем увидеть в настоящее время только на последних процессорах Intel Xeon. Для этого выставим в RMClock режим управления производительностью процессора (P-State Profile) Minimal, предварительно выставив минимальные значения FID/VID как 14x и 1.2V, соответственно.

Результат налицо: эффективная частота снизилась до ~2.8 ГГц, FID/VID — до запрашиваемых значений 14x и 1.2V. Технология C1E при этом как бы отключилась — естественно, снижать эффективную частоту процессора, равно как и его напряжение, дальше некуда. Пойдем дальше: выставим профиль производительности процессора Maximal (FID = 18x, VID = 1.388V).

Поведение процессора в этом режиме весьма интересно: несмотря на принудительное выставление максимальных FID/VID, C1E явно «берет верх» над Enhanced SpeedStep — эффективная частота процессора снижается, FID и VID колеблются между минимальном и максимальном уровнями. Т.е. теперь «как бы отключилась» не C1E, а DBS. Проведем еще один эксперимент: оставим режим производительности Maximal, но… снизим до минимума питающее напряжение (в отсутствие загрузки процессора это вполне можно сделать), т.е. выставим FID/VID как 18x и 1.2V.

Вот теперь C1E действительно отключилась, полностью передав управление технологии DBS. Отсюда можно сделать интересный вывод: для того, чтобы технология C1E могла функционировать, напряжение процессора (VID) должно, пусть даже на самую малость (0.0125В), но отличаться от минимально возможного (задаваемого в TM2 Target VID). Иными словами, под различными состояниями производительности/энергопотребления процессора для C1E в первую подразумеваются значения VID, а значения FID для нее вторичны.

Подводя итоги

В нашей предыдущей статье мы начали, а в настоящей — завершили рассмотрение современных технологий управления производительностью и энергопотребления процессоров Intel Pentium 4 (Prescott) и Intel Xeon (Nocona). Основной вывод уже был сделан ранее — все рассмотренные технологии, начиная с первой ODCM, и заканчивая последними Enhanced SpeedStep (DBS) и Enhanced Halt State (C1E), по всей видимости, имеют в своей реализации общую идейную основу — модуляцию тактовой частоты процессора (цикла полезного действия). Может показаться, что это — своего рода «нечестность», обман потребителя. Разумеется, это не так, и мы не утверждали ничего подобного. На самом деле, это — всего лишь один из возможных (и наиболее простых) способов реализации упомянутых технологий, но он не менее эффективный, чем «более честные» способы. К тому же, не следует забывать, что это одна из возможных точек зрения (автора статьи), с которой можно и не соглашаться. Можно придумать и альтернативную точку зрения, гораздо более «правильную» с точки зрения официальной документации Intel.

Какова же возможная альтернатива? Можно предположить, что, поскольку некоторые блоки процессора (например, арбитры шины, асинхронные префетчеры и пр.), скорее всего, не могут легко осуществлять переход между различными скоростями функционирования, инженеры Intel, скорее всего, «разделили» процессорное ядро на несколько независимо тактируемых составляющих (либо за счет нескольких PLL, либо за счет делителей частоты, преобразующих опорную тактовую частоту). Часть из этих составляющих всегда функционирует на полной частоте (в эту часть попадает и Time Stamp Counter, на показаниях которого основан общепринятый метод измерения тактовой частоты процессора), тогда как остальные части (исполнительные модули) могут тактироваться меньшей частотой. При этом, правда, не совсем понятно, зачем инженеры Intel решили тактировать TSC полной частотой, тогда как счетчики производительности процессора (Performance Monitoring Counters, PMC) работают на «уменьшенной» частоте?

Возможные объяснения этого факта, равно как и выбор между представленными точками зрения оставим на откуп читателю. Со своей стороны отметим, что в ходе нашего исследования нам не удалось обнаружить каких-либо экспериментальных свидетельств в пользу второй, более «официальной» гипотезы. Разумеется, у нас нет явных свидетельств и в пользу нашей точки зрения, за исключением того, что она не противоречит экспериментальным фактам. Поэтому займемся «доказательством от противного». Среди основных возражений против нашей точки зрения можно наметить, во-первых, некорректность методики определения частоты процессора, а во-вторых, фактически, наше заявление о том, что процессоры Pentium 4 и Xeon могут работать на полной частоте при пониженном напряжении питания (в режимах TM2, DBS и C1E).

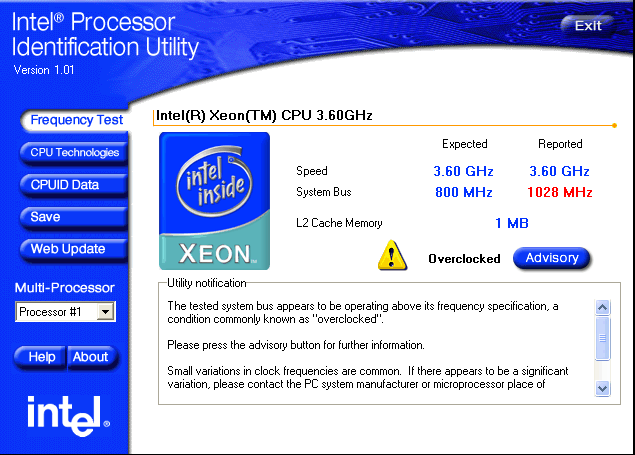

Начнем с первого утверждения. Корректность определения фактической частоты процессора не вызывает сомнений — этим методом пользуются все без исключения системные утилиты (CPU-Z, WCPUID), наконец, сама операционная система, а также… Intel Processor Identification Utility! Приведенный ниже скриншот получен на процессоре Intel Xeon 3.6 ГГц при включении технологии Enhanced SpeedStep.

Мы полагаем, картина не требует пояснений: частота процессора измерена утилитой по TSC (3.6 ГГц), а частота системной шины — простым делением ее на текущий «коэффициент умножения» 14x, что приводит к неправильному конечному значению 1028 МГц и красноречивой надписи «Overclocked!». Итак, если «неправильным» методом пользуются и утилиты Intel, что же тогда следует считать «правильным» методом? Применение формул вида

FSB_freq = TSC_freq / Startup_FID

CPU_freq = FSB_freq * Current_FID,

т.е. банальное умножение частоты системной шины процессора на текущий «коэффициент умножения»? (именно этот метод, по всей видимости, использовался при демонстрации технологии DBS на IDF 2004 Russia) Извините, но это уже не подлинное измерение, а натуральный подгон, выдача желаемого за действительное. К тому же, этот метод будет явно не универсальным, т.е. непригодным для любого x86-совместимого процессора.

Перейдем ко второму утверждению. На первый взгляд, оно очевидно: снижение питающего напряжения процессора (при срабатывании TM2, а также задействовании Enhanced SpeedStep и Enhanced Halt State) непременно должно сопровождаться снижением реальной тактовой частоты процессора. Но это лишь на первый взгляд — факты говорят совсем о другом. Прежде всего, взглянем на последний скриншот в предыдущем разделе — по нему четко видно, что процессор Intel Xeon 3.6 ГГц способен работать на полной частоте (FID = 18x) и при весьма низком напряжении питания — 1.2V (на 0.1875V ниже номинального!). А во-вторых, проведем еще один интересный эксперимент — возьмем «разблокированный» процессор Intel Pentium 4 560J (Prescott) 3.6 ГГц и заставим его считать, что он работает на минимальной тактовой частоте (FID = 14x), но… повысим частоту системной шины до 266 МГц (как это сделать, мы подробно описали в статье «Раскрываем потенциал DDR2-533. Часть 2: частота FSB 266 МГц, процессор Intel Pentium 4 Prescott»).

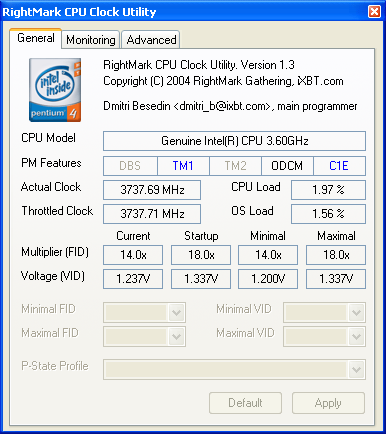

Смотрите, что происходит: процессор «уверен», что он по-прежнему работает в штатных условиях, в связи с чем динамически управляет своим питающим напряжением в режиме простоя благодаря технологии C1E. Тогда как его реальная частота — как подлинная, так и эффективная — равны 3.74 ГГц. Получается, что процессоры Pentium 4 и Xeon действительно могут работать на полной частоте при пониженном напряжении питания, если они находятся в режиме простоя (C1/C1E).

Таким образом, приведенные выше факты, хотя и явно не подтверждают, но дополнительно подкрепляют наш вывод о единой основе реализации функций управления производительностью и энергопотреблением процессоров Intel Pentium 4 и Xeon.