Всё, что вы хотели знать о микроэлектронике, но почему-то не узнали… Часть 2-я

Оглавление

Часть 1-я: Как всё начиналось — 1940–1989, а также о первых 1-кристальных процессорах.

Часть 2-я: Наши дни — 1990–2010, а также пример современного техпроцесса.

Часть 3-я: Анализ и перспективы — 70 лет микроэлектроники в таблицах и графиках, новый шаг Intel, макрохитрости микроэлектроники, и о будущем.

Наши дни

1990-е

Современный литографический сканер ASML TwinScan 1950i. Луч лазера, пройдя через многочисленные линзы и движущуюся взад-вперёд маску (её каретка видна справа от надписи TwinScan) попадает на каретку с экспонируемой пластиной, которая также движется, но уже в двух координатах, подставляя под луч новую порцию поверхности. Вторая каретка со следующей «вафлей» в этот момент проходит подготовительную стадию, в которой различные оптические датчики изучают малейшие неровности этой конкретной пластины, чтобы далее оптимизировать её экспонирование — двухстадийный конвейер. Слева от рабочей зоны видны входной и выходной порты для контейнеров с пластинами по 25 штук в каждом, а сверху (между надписью и кареткой маски) — банк масок, подставляющий нужную для данной экспозиции и имеющий собственный небольшой порт. «Светофор» — это индикатор состояния, встроенный почти в каждую установку в «чистой комнате» фаба. В движении всё это можно посмотреть тут. |

До 90-х гг. фотолитография использовала ртутные газоразрядные лампы, отсекая из их света всё, кроме нужной частоты, совпадающей с одним из пиков («линий») — G (436 нм), H (405) или I (365). После того, как мощности ламп стало не хватать для требуемой производительности, потребовалось внедрить эксимерный лазер, что сделали в 1982 г. в IBM (сам такой лазер изобретён в СССР в 1971 г.). В зависимости от газа он даёт длину волны 248 (KrF), 193 (ArF) и 157 нм (F2). От фторовых лазеров, правда, отказались из-за чрезвычайных технических проблем, решение которых не окупится преимуществами — дело в том, что сам воздух начинает поглощать излучение с длиной волны меньше 186 нм, так что весь литограф надо переделать под вакуум. Это его усложняет и удорожает с 40 до 50 млн. долларов, а сканеров фабу требуется несколько. Поэтому даже самые современные техпроцессы с технормами менее 30 нм всё ещё используют аргон-фторовый лазер. При этом переход на так называемый экстремальный ультрафиолет (ЭУФ, EUV) с длинами волн 13,5 нм и менее рано или поздно всё равно состоится — и без вакуума тут точно не обойтись.

Тут надо сказать, почему формирование рисунка на поверхности приобретает большие сложности, когда его размер оказывается меньше длины волны экспонирующего света. Строго говоря, законы волновой оптики не запрещают формирование деталей с таким разрешением. Но начиная с этих размеров линейная оптика заменяется на куда более сложную дифракционную, требующую большую точность при всех операциях — с соответствующим влиянием на цены установок. С точки зрения теории стоит познакомиться с эмпирическим критерием разрешения Рэлея (о минимальном угловом расстоянии между точками), числовой апертурой (NA) и технологическим параметром k1. Тут укажем лишь, что этот k1 в идеале может опускаться до 0,25, но насколько конкретная установка и техпроцесс приближены к идеалу — зависит от их продвинутости.

OPC: требуется вычислить такую маску (зелёный контур), чтобы получаемый ею символ (красный) оказался как можно ближе к требуемому (синий). Без коррекции толщина линий символа окажется больше или меньше в разных частях, в т. ч. за счёт влияния соседних линий. Это может привести как к разрыву дорожки, так и к замыканию пары дорожек. |

Одна из таких продвинутых методик — вычислительная литография: использование масок, рисунок которых вычислен с учётом волновых свойств света с целью добиться большего разрешения или меньших искажений при данной длине волны. Первые подобные программы были написаны в начале 80-х и использовались лишь для оптимизации рисунка маски, т. к. недостаток вычислительной мощности позволял моделировать площадь всего в несколько квадратных микрон. К 1998 г., когда замаячил переход на 180 нм (первый техпроцесс с технормой меньше длины волны), мощность компьютеров уже сильно возросла, что позволило использовать более точные алгоритмы и модели. Для современных технорм требуются уже тысячи процессоров и недели расчётов, чтобы вычислить рисунки для десятков масок, необходимых самых сложным ИС.

К основным методам вычислительной литографии относятся фазосдвигающие маски (PSM) и оптическая коррекция близости (OPC). Используемая с 90-нанометрового процесса (2006 г.) технология PSM — это коррекция толщины отдельных «пикселей» маски для изменения их прозрачности, что меняет фазу проходящего сквозь них света. Учитывая волновые свойства, это позволит (не считаясь с длиной волны) экспонировать на фоторезисте рисунок, отдельные элементы которого либо усилены синфазным наложением волновых пиков, либо удалены противофазным — это увеличивает разрешение, приближая тот самый параметр k1 к идеалу. Более современная OPC искажает рисунок маски для компенсации ошибок получаемого изображения из-за дифракции падающих волн. OPC нужна уже не для увеличения разрешения, а для исправления искажений одиночных структур, форма которых при таких размерах получается куда хуже, чем если бы элементы были регулярными.

Микроэлектронщики давно хотели использовать медные межсоединения вместо алюминиевых, т. к. удельное сопротивление меди меньше. Это значит, что «медные» чипы меньше выделяют тепла и быстрее работают, т. к. меньшая часть коммутируемого транзисторами тока уйдёт в нагрев, а не в переключение других транзисторов. Однако если в линиях электропередач и прочих проводах медь применяется давно, то микроэлектроника не могла внедрить столь полезный металл десятки лет. Причина в том, что после осаждения меди при дальнейших процессах нагрева она диффундирует (внедряется) в подлежащие элементы, особенно в кремний, что даже получило термин «медное отравление».

В 1997 г. IBM наконец-то решила задачу. Сначала медь надо осадить. Но из-за её химической стойкости её нельзя протравить плазмой сквозь окна в фоторезисте (не удалив при этом оставшуюся, т. е. маскирующую часть самого резиста), как это делается для алюминия. Вместо это применяется «дамасская работа» (damascene): процесс, похожий на изготовление булатной стали с мелким орнаментом. Сначала в изоляторе протравливаются канавки для дорожек. Далее вся поверхность выстилается барьерным металлом (который чаще всего оказывается нитридом титана или вольфрама, что, строго говоря, относится к керамике), не допускающим диффузии, но пропускающим ток. Его толщина должна быть небольшой, т. к. его сопротивление всё же больше, чем даже у алюминия.

Химико-механическая планаризация: вращающийся подвес прижимает пластину лицевой стороной к вращающемуся диску с наносимой на него пастой. Специальный диск-восстановитель (не показан) выравнивает пасту. Восстановитель и подвес также могут двигаться вдоль радиуса. |

Далее на всю поверхность осаждают толстый слой меди, переполняющий канавки. Т. к. плазмохимическое травление (оно же — реактивное ионное травление, RIE) не подходит, используется химико-механическая планаризация (ХМП или CMP). До 90-х гг. она считалась слишком грязной и дефектной для тонкого производства, т. к. абразивные частицы полировальной пасты создавали острые осколки стираемого слоя, да и сама паста неидеально чистая. Но для медного слоя ХМП оказалась лучше имеющихся способов, т. к. процесс полировки металла останавливается на границе с изолятором (точнее, с его невытравленными частями, находящимися выше дна канавок). В результате на чипе остаётся очень плоский слой с внедрёнными медными дорожками, не выходящими по высоте из окружающего изолятора. Более того, так называемое двойное воронение позволяет одновременно получить ещё и вертикальные проводящие окна, соединяющие текущий слой с предыдущим. Сверху всё покрывается ещё одним барьерным слоем, излишки которого вытравливаются над внутрислойным изолятором, но не над дорожками. После этого можно осаждать уже межслойный изолятор для следующего проводящего слоя.

КНИ в чипе IBM (для наглядности пространство между проводниками вытравлено). Снизу вверх: подложка, оксид-изолятор, тонкий слой кремния, транзисторы и один слой металлических межсоединений с опущенными до транзисторных выводов металлизированными окнами. |

Ещё одно достижение изначально было связано с радиационно-стойкой электроникой, необходимой в авиакосмических и атомных отраслях. При уменьшении размера транзистора он оказывается всё более чувствителен к высокоэнергетическим частицам, способным вызвать ошибку в схеме. Чтобы усилить защиту, в 1963 г. придумали применять не кремниевую, а сапфировую пластину, на которую осаждён тонкий слой кремния — КНС (кремний на сапфире) или SOS. Оказалось, то такая конструкция сильно уменьшает подзатворные утечки, а значит — и потребление энергии, а также снижает паразитную ёмкость, что повышает частоту. Однако выращивание сверхчистой сапфировой болванки оказывается куда дороже выращивания кремниевой, поэтому «в массах» такой вариант не прижился.

Но в 1998 г. IBM анонсировала технологию кремния на изоляторе (КНИ, silicon on insulator, SOI): на кремниевой пластине формируется слой оксида кремния (изолятора), а поверх него — тонкий рабочий слой кремния. Строго говоря, КНС тоже относится к КНИ, т. к. сапфир (оксид алюминия Al2O3) также является изолятором. Но кремниевый КНС дешевле и лучше приспособлен к имеющемуся оборудованию. Учитывая преимущества, можно предположить, что за 13 лет вся полупроводниковая промышленность давно перешла на КНИ-пластины. Однако мировой лидер этой самой промышленности, компания Intel, будто в упор их не замечает и продолжает использовать «bulk silicon», т. е. чистые кремниевые пластины, т. к. они ещё дешевле. К этому заявлению мы ещё вернёмся…

2000-е

Кремний до и после осаждения на кремний-германиевый слой. |

В 2001 г. IBM изобретает напряжённый кремний (strained silicon) — формирование слоя кремния для канала, в котором расстояние между атомами (как минимум в направлении исток-сток) не равно естественному шагу кристаллической решётки (543 пм). Для большего шага сначала внедряется «посевной» слой кремния-германия. Кристалл германия имеет шаг атомов 566 пм. Смешанный полупроводник сохраняет это значение, даже если доля германия всего 17% (это для 90 нм; а для 32 нм — уже 40%). Осаждаемые поверх атомы кремния межатомными силами крепятся к атомам широкой решётки и остаются с её шагом, формируя канал. Разряжение атомов увеличивает подвижность электронов, что ускоряет n-канальный транзистор на 20–30%. Кстати, именно из-за большей подвижности электронов германий первым стали применять в электронике.

В 2004 г. эту технологию применили Intel и AMD для техпроцесса 90 нм. Для 65 нм внедрена ионная имплантация германия и углерода в исток и сток. Германий раздувает концы транзистора, сжимая его канал, что увеличивает скорость дырок (т. е. основных носителей заряда в p-канальных транзисторах). Углерод, наоборот, сжимает исток и сток, что растягивает n-канал, увеличивая подвижность электронов. Также весь p-канальный транзистор покрывается сжимающим слоем нитрида кремния. Применяются и растягивающие покрытия.

Структурирование распорками (сверху вниз): формирование первичного шаблона фоторезистом (оранжевый), осаждение химической маски (зелёная), формирование распорок направленным (вертикальным) травлением, удаление резиста, травление рабочего слоя (синий), удаление распорок. |

В 2006 г. только что внедрённый техпроцесс 65 нм уже не мог основываться лишь на вычислительной литографии, т. к. с длиной волны 193 нм её уже не хватало. Решение, основательно обновившее мировое чипостроение — множественное структурирование, более известное по своей простейшей реализации — двойное структурирование (double patterning). Это семейство технологий снижает минимальный экспонируемый размер увеличением числа экспонирований. Как правило, в самых современных техпроцессах применяются несколько приёмов из этого арсенала.

Самосовмещёные распорки (self-aligned spacers) позволяют получить вдвое большее разрешение формируемого рисунка при той же технорме: вначале на боковые стенки фоторезиста налипает специальная химическая маска, используемая далее как финальный шаблон травления после удаления резиста. Разумеется, этот приём можно повторять и далее, используя вторичный шаблон для изготовления третичного с ещё вдвое большим разрешением — насколько это позволит химическая устойчивость материалов и повторяемость процессов.

Второй случай, требующий применения нового резиста, — двойное (кратное) экспонирование (double (multiple) exposure): вторая маска экспонируется на тот же резист со смещением относительно первой на величину технормы, причём пластина даже не покидает литограф. Чтобы второй рисунок добавился к первому (а не частично наложился на него), требуется, чтобы оба раза формировались детали шириной меньше технормы. Таким образом, например, формируются линии металла и поликремния — сначала все «вдоль», потом все «поперёк». Замена двухмерного рисунка двумя одномерными упрощает его нанесение.

Ещё один вариант двойного экспонирования (применяется начиная с 32 нм) использует два разных вида резиста. Второй наносится на рисунок, сформированный в первом, облучается через вторую маску, после чего удаляется незафиксированная часть второго резиста, но так, чтобы не повредить рисунок первого. И тут нужна продвинутая химия — новые резисты, боковое травление для уменьшения ширины и пр. Зато, теоретически, такая методика позволяют формировать сколь угодно мелкие детали. Например, 22-нанометровые элементы могут получаться перемежением двух масок на 45-нанометровом литографе, трёх масок на 65- или четырёх на 90-нанометровом. Т. е. текущий техпроцесс можно «разогнать» до следующего за счёт увеличения числа масок и производственных стадий — с очевидным удорожанием стоимости завода и внедрения производства новых микросхем. Но с недавних пор это всё равно оказывается дешевле «честного» уменьшения технормы через литографию.

Очевидными недостатками кратного экспонирования является кратное увеличение числа масок и технологических операций для формирования каждого критического слоя, а также очень высокие требования по точности совмещения масок. Небольшое смещение между двумя экспозициями слоя может привести, например, к асимметрии истока и стока (относительно затвора) у всех транзисторов пластины.

В 2006 г. появилось ещё одно улучшение — погружённая литография. Впрочем, в крайне неустойчивой и неполной русскоязычной терминологии по странной традиции прижилась транслитерированная форма оригинала — иммерсионная литография. Суть оной в том, что пространство между последней линзой и экспонируемой пластиной заполняется не воздухом, а жидкостью (на данный момент — водой). Это улучшает разрешение на 30–40% ввиду большего преломления жидкости, которое влияет на вышеуказанный параметр NA, равный 1 для воздуха и 1,33 для воды. Intel внедрила иммерсионную литографию вместо «сухой» с техпроцесса 32 нм, а AMD — ещё с 45 нм. Интересно, что первые «водные» сканеры появились ещё в 2005 г., но техпроцессы с ними пришлось дорабатывать около года после внедрения на фабах до применения в массовом производстве. И вот почему:

Мало того, что вода должна быть сверхчистая (она и так требуется почти в половине технических процессов производства ИС) — в ней не должно быть пузырьков, температура должна быть равномерной, она не должна сверх меры загрязняться и поглощаться фоторезистом или растворять его. Более того, 193-нанометровый ультрафиолет ионизирует воду — а выбитые электроны могут испортить фоторезист. Решить все эти вопросы удалось нанесением прозрачного гидрофобного защитного покрытия на фоторезист перед экспонированием. Таким образом плотность дефектов осталась примерно та же.

Иммерсионная литография. |

Не менее важная часть — производительность, ведь мало изготавливать чипы сложными и дешёвыми, их нужно много. Скорость пластины в литографическом сканере достигает 0,5 м/с, но держать её всю под слоем воды не выйдет — сверхточное позиционирование каретки с пластиной полагается на лазерные интерферометры, и малейшая рябь на поверхности воды всё испортит. Поэтому слой «привязали» к оптике. Чтобы пластина не уносила воду в сторону, вокруг оптики разместили водяные микросопла, половина из которых по ходу движения впрыскивают воду, а противоположные им — высасывают. Всё это происходит с очень точным контролем, чтобы не внести пузыри при впрыске и не оставить позади капли после отсоса, что особенно трудно с краю пластины. Теперь ясно, почему иммерсионный сканер гораздо дороже сухого.

В 2007 г. (для техпроцесса 45 нм) в микроэлектронике появилось сокращение HKMG — High-k [dielectric and] Metal Gate, т. е. изолятор с высокой диэлектрической проницаемостью и металлический затвор. Сначала о первой половине формулы. Параметр k означает относительную диэлектрическую проницаемость (безразмерную величину, разную для разных веществ), однако в английском языке (и, к сожалению, в большинстве русских переводов) её почему-то называют диэлектрической константой. (Не говоря уже о том, что вместо «k» должна быть греческая буква каппа — κ…) Настоящая же диэлектрическая константа (она же — электрическая постоянная, ε0), как и полагается, неизменна. В микроэлектронике «нормальным k» считается 3,9, что соответствует проницаемости диоксида кремния (SiO2), десятилетия использовавшегося в качестве боковых, межслойных и подзатворых изоляторов. Вещества с проницаемостью выше 3,9 относятся к классу high-k (высокопроницаемые), а ниже — к low-k (низкопроницаемые).

Последние нужны для межслойных и боковых диэлектриков, т. к. таким образом можно лучше изолировать металлические дорожки межсоединений, избегая диэлектрического пробоя из-за слишком тонкого слоя изоляции между ними. Сама же изоляция должна быть тонкой, т. к. иначе невозможно подвести дорожки к всё время уменьшающимся транзисторам, кроме как сделав такими же малыми и проводники, и разделяющие их изоляторы. К низкопроницаемым материалам относятся диоксид кремния-углерода (органосиликатное стекло с k=3 — самый популярный диэлектрик, используемый с 90 нм), он же, но пористый (k=2,7), нанокластерный кварц (2,25) и некоторые органические полимеры (k<2,2). По идее, изолятор, разделяющий затвор и канал транзистора, должен подчиняться этим же требованиям, но на деле оказывается всё наоборот — тут нужен как раз высокопроницаемый диэлектрик.

Всё дело в эффекте квантового туннелирования. К 90-нанометровому техпроцессу толщина затвора уменьшилась до величины от 1,2 (у Intel) до 1,9 нм (у Fujitsu; обе цифры — для n-каналов). А шаг кристаллической решётки кремния, напомним, равен 0,543 нм. При такой тонкости электроны начинают туннелировать сквозь изолятор, приводя к утечке тока. Дело обстояло настолько серьёзно, что для техпроцесса 65 нм уменьшились все параметры транзистора, кроме толщины затвора, т. к. если бы его сделали ещё тоньше, то ни о какой энергоэффективности не стоило бы и мечтать.

Графики толщины подзатворного изолятора в SiO2-эквиваленте и относительной утечки тока. Введение высокопроницаемых изоляторов для техпроцесса 45 нм позволило уменьшить эквивалентную толщину, увеличив физическую, чтобы уменьшить утечки для увеличения скорости. |

Высокопроницаемый диэлектрик позволяет электрическому полю затвора проникать на большую глубину или толщину, не снижая остальные электрические характеристики, влияющие на скорость переключения транзистора. Так что, заменив применявшийся с 90-х гг. оксинитрид кремния на новый оксинитрид кремния-гафния (HfSiON, k=20–40) толщиной в 3 нм, для процесса 45 нм удалось уменьшить утечки тока в 20–1000 раз. Для получения такой же скорости работы старый затвор пришлось бы делать толщиной в 1 нм, что было бы катастрофой. Встречающиеся сегодня цифры толщин подзатворных изоляторов менее чем в 1 нм являются как раз такими SiO2-эквивалентами и применяются только для вычисления частоты, но не утечки. Диоксид кремния, впрочем, до сих пор имеется в виде нижнего подзатворного слоя, но используется только как физический интерфейс для совместимости с текущими техпроцессами.

Любопытно, что при анонсе нового материала Intel поблагодарила старого микроэлектронного соперника — IBM. Но не потому, что инженеры «синего гиганта» разработали для коллег с не менее синим логотипом новый материал — а потому, что детальное математическое моделирование, доказавшее, что именно гафний является оптимальным материалом, провели на суперкомпьютере IBM. Учитывать пришлось не только проницаемость, но и ширину запрещённой зоны (она должна быть согласована с кремнием), морфологию слоя, термостабильность, ненарушение высокой подвижности носителей заряда в канале и минимальность краевых дефектов.

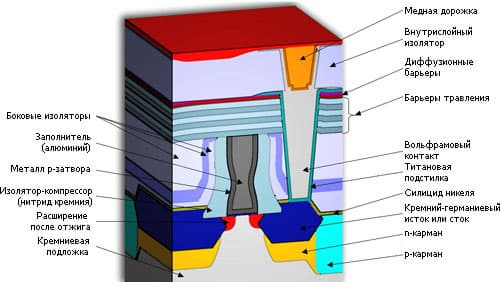

Впрочем, одного недостатка избежать не удалось: гафниевый изолятор не совместим с поликремниевым затвором, так что пришлось менять и его — на металлический. Теперь ясно, почему эти две технологии идут парой. Однако новый затвор не алюминиевый, как это было в 60-х, а в виде сплава двух металлов. Его сопротивление ниже, что ускоряет переключение транзистора. Изначально было известно лишь то, что сплав отличается для p- и n-канальных транзисторов, причём Intel (которая первой всё это применила) держит оба состава в строгом секрете. Однако через год (в 2008-м) инженеры IBM (работа которых с тех пор используется в т. ч. на заводах GlobalFoundries, ранее принадлежавших AMD) сделали свою версию этой технологии, так что деталями пришлось делиться и Intel.

До сих пор использованию металлов мешал тот факт, что после имплантации примесей пластина проходит отжиг при температуре 900–1000 °C, что выше температуры плавления многих металлов (включая алюминий) и сплавов, но не поликремния. Хотя даже и без плавления при повышении температуры металл может диффундировать в подлежащие слои. Теперь ясно, почему точная формула сплавов держится в секрете — их действительно трудно подобрать. Не зря лично Гордон Мур назвал HKMG наибольшим достижением с момента изобретения поликремниевого затвора в 1969 г. До этого момента алюминиевые затворы никому не мешали, т. к. не было ни высокотемпературного отжига, ни формирования истоков и стоков впритык к затворам. Сегодня же приходится применять всё более экзотические материалы — например, Panasonic легирует сплав для n-каналов своих HKMG-транзисторов редкоземельным элементом лантаном.

Варианты реализации металлического затвора — последним (слева, Intel) или первым (справа, общий случай). Стадии травления и полировки не показаны; также не указан барьерный слой между подзатворным изолятором и самим затвором (у Intel — TiN и TiAlN для p- и n-каналов, у GF — AlO). Версия IBM и GF для всех транзисторов использует одинаковые заполнитель (NiPtSi) и даже рабочий «металл» (TiN) — но для n-каналов они легируется мышьяком. |

Не меньше вопросов возникает при обсуждении двух версий технологии. Intel сначала формирует обычный поликремниевый затвор, работающий лишь как маска для создания истока и стока, затем вытравливает его, осаждает сплав для p-каналов, удаляет его из n-транзисторов, осаждает сплав для n-каналов и добавляет ко всем затворам алюминиевый заполнитель — этот вариант называется Gate last, «затвор последним». IBM и GF используют Gate first, «затвор первым»: на подзатворный изолятор осаждается p-сплав, удаляется над n-каналами, осаждается n-сплав, удаляется над p-каналами, осаждается поликремний в качестве заполнителя и маски — а далее как обычно.

Intel утверждает, что её версия лучше совместима с напряжённым кремнием (потому что ему не мешает металл затвора) и позволяет использовать большее разнообразие металлов (потому что они осаждаются после высокотемпературных обработок), тогда как у конкурентов сложнее получить разные виды транзисторов (по нагрузке, скорости, напряжению и пр.), и они всё равно окажутся чуть медленнее и с меньшим выходом годных. IBM и GF отвечают, что их способ дешевле и требует меньших ограничений на расположение транзисторов, что позволяет разместить их на 10–20% плотней, а в Intel приходится мириться с жёсткими ограничениями на размеры и расположение. Причём Intel тут в меньшинстве, потому что «затвор первым» формируют и в Chartered, Freescale, Infineon и Samsung. Последняя, правда, недавно заявила, что для её 20-нанометрового процесса затвор всё же будет «последним».

4 стадии цикла молекулярного наслаивания AlO2. Алюминий (синие атомы) поставляет 1-й прекурсор, валентные связи которого заняты лигандами (временными радикалами, в данном случае метильными группами —CH3). 1-я продувка удаляет метан (CH4) и избыток прекурсора. Вторым прекурсором является вода, замещающая остальные два лиганда у каждого атома Al. 2-я продувка удаляет лишнюю воду и метан. В следующем цикле атомы водорода 1-го слоя будут замещены связью с Al 2-го слоя, восстановив свободные метильные группы до метана. |

Формирование широко применяемых в современных чипах тонких плёнок было бы невозможно без технологии молекулярного наслаивания, она же — послойное атомное осаждение (Atomic Layer Deposition, ALD). Её суть заключается в том, что за один цикл обработки, длящийся всего несколько секунд, образуется ровно один слой молекул, так что толщину откладываемой плёнки можно регулировать с максимальной возможной точностью (для самых простых веществ — ±10 пм) лишь числом циклов. Каждый цикл состоит из двух стадий осаждения из газовой фазы прекурсоров (химических предшественников осаждаемого вещества) и двух продувок для удаления излишков. Прекурсоры подбираются так, чтобы лишь один их слой мог прилипнуть к уже осаждённому материалу — к подложке для 1-го осаждения, к предыдущему слою для нечётных осаждений (после 1-го) или к первому прекурсору для чётных. Способ подходит не только для составных веществ, но и для некоторых чистых металлов.

Молекулярное наслаивание впервые опробовано в начале 60-х профессором Станиславом Кольцовым из Ленинградского Технологического Института имени Ленсовета (ныне — СПбГТИ), а сама идея предложена профессором Валентином Алесковским в 1952 г. в его докторской диссертации «Остовная гипотеза и опыт синтеза катализаторов». Во всём остальном мире наслаивание появилось лишь в 1977 г. под именем «Atomic Layer Epitaxy» (ALE). Однако до микроэлектронного применения дело дошло лишь в середине 90-х — до этого очень тонкие плёнки были не нужны. Сейчас же, когда отдельные части транзистора исчисляются единичными атомными слоями, без ALD не обойтись. Тем страннее то, что в русской части Википедии об этой технологии и её создателях не написано вообще ничего, да и в остальном рунете — с гулькин нос…

Расскажем и о двух любопытных техниках, применяемых лишь некоторыми компаниями. Впрочем, первая известна с начала 2000-х и в какой-либо форме применяется во всех современных сканерах — структурный свет (structured light), меняющий форму луча лазера. Его сечение при этом оказывается не круглым, а кольцевым, 4-полюсным или каким-то ещё. Однако в 2009 г. Toshiba и NEC использовали в своём 32-нанометровом процессе новый вид такого освещения (возможно, в комплексе с доводкой методов OPC под него), что позволило обойтись без дорогостоящего двойного структурирования (которое у этих фирм вызвало 25-процентное увеличение дефектности). Обычно на таких размерах одно экспонирование единственной маски на слой приводит к сильным искажениям прямых дорожек (не смотря на OPC). Но структурный свет решает эту проблему и даже позволяет уменьшить шаг между элементами. Поэтому у Toshiba и NEC получилась самая маленькая (среди 32-нанометровых процессов всех фирм) ячейка СОЗУ — на 0,124 мк² (позже мы сравним эти цифры детальней), а плотность транзисторов в логике — 3,65 млн. вентилей/мм². И всё это по вдвое меньшей удельной цене, чем для своих же 45 нм, и на 9% дешевле, чем с применением двойного структурирования. Учись, Intel :)

«Воздушные» (т. е. вакуумные) зазоры между проводниками 5-го и 7-го металлических слоёв. |

В том же 2009 г. IBM реализовала в массовом производстве технологию воздушных зазоров (Airgap) в качестве внутрислойных изоляторов, разделяющих медные проводники одного слоя. Состоит такой диэлектрик из тонкостенных пузырей размером в 20 нм, стенки которых собираются из полимера методом самосборки. Пузыри содержат, вопреки названию, не воздух, а вакуум — идеальный изолятор с проницаемостью, равной 1 (впрочем, у воздуха почти столько же). По заявлению IBM, с уменьшением межпроводной ёмкости чип потребляет на 35% меньше энергии или работает на 15% быстрее. Впрочем, почувствовать это могли лишь покупатели серверов IBM с ЦП архитектуры POWER. «Могли», потому что в 32-нанометровом процессе IBM воздушные зазоры исчезли — видимо, механическая прочность «дырявого» слоя оказалась слишком малой для его достаточно низкодефектной планаризации.

Пример современного техпроцесса

Устройство 45-нанометрового p-канального транзистора в микросхемах Intel. Тут не указано присутствие в затворе слоя металла для n-канального транзистора. |

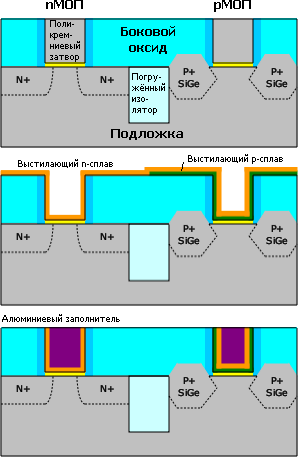

Чтобы подытожить всё вышенаписанное, приведём описание «скоростного» 45-нанометрового техпроцесса Intel как одного из наиболее изученных:

- используется пластина из цельного кремния (не КНИ) и сухая литография на 193 нм с двойным структурированием;

- длина затвора — 35 нм (как и в 65-нанометровом процессе);

- шаг затвора — 160 нм без изоляторов (на 27% меньше, чем в 65-нанометровом) и 200 нм с ними (на 9% меньше);

- осаждение металлического «затвора последним»;

- спрямление углов затвора с помощью покрытия вторым видом фоторезиста;

- эквивалентная толщина высокопроницаемого подзатворного изолятора — 1 нм;

- для улучшения подвижности дырок у p-канальных транзисторов легирование германием истока и стока увеличено с 23 до 30%, что в совокупности увеличило частоту на 51%;

- сонаправленные по всему чипу каналы;

- 10-слойные межсоединения (начиная со 2-го слоя — медные) с изолятором из легированного углеродом диоксида кремния, включая размещённый на истоках и стоках «нулевой» слой вольфрама, также служащий диффузионным барьером;

- почти везде чётные слои металла параллельны каналам, нечётные — перпендикулярны;

- последний, наиболее толстый слой металла работает как термо- и энергораспределитель для всего кристалла;

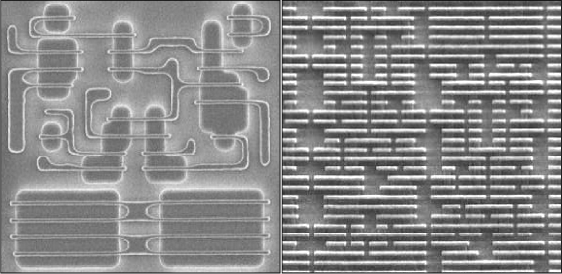

- обильное использование фиктивных структур (дорожек и затворов) для выравнивания локальной плотности и теплопроводности;

- бессвинцовая пайка кристалла в корпус.

На одной 300-миллиметровой пластине умещается 568 процессоров Core 2 Duo с 6 МБ кэша L2, изготовленных по технорме 45 нм. Средний темп выхода пластин при производстве на фабах Intel — ≈20 мин. на лот (25 пластин). Проверить пластину на сбойность менее чем за 50 секунд полностью не получится, поэтому применяется быстрая оценка состояния транзисторов. Для этого в свободных местах каждого будущего кристалла расположены десятки простейших осцилляторов (чёрные точки), транзисторы которых имеют те же параметры, что и для окружающей логики или кэшей. Замерив частоты каждого осциллятора и зная их расположение, для каждого процессора строится карта отклонений параметров транзисторов. Тут на ней зелёным обозначены средние параметры, жёлтым и красным — замедленные, а голубым и синим — ускоренные. После разрезания пластины на отдельные кристаллы те, которые после оценочных тестов признаны хоть на что-то годными, отправляются на сборочный завод. Там они корпусируются, проходят программирование прошивки, детальное тестирование, отключение неработающих, медленных или слишком прожорливых частей (если требуется) и присваивание множителей и напряжений. | |

4 последних поколения транзисторов Intel (слева направо, сверху вниз) — 90 (2003 г., первое применение напряжённого кремния), 65 (2005), 45 (2007, первое применение комбинации HKMG) и 32 (2009) нм. | |

65-нанометровые транзисторы (слева) могли себе позволить такие роскошества как двунаправленные дорожки (вертикали и горизонтали) и переменные размеры затворов и их шагов. Для 32-нанометрового техпроцесса (справа) всё это запрещено. | |

Видео о внутреннем устройстве фабрики фирмы Infineon. А вот полурекламный ролик про интеловский Фаб-32: |