Разбор устройства процессора AMD EPYC 9004

В этой статье будет разбираться устройство процессоров AMD на базе микро архитектуры Zen 4 на примере процессора AMD EPYC 9004. В данном посте будет разобран пример схемы процессора, будет разобрано ядро процессора и устройство технологии AMD 3D V-Cache

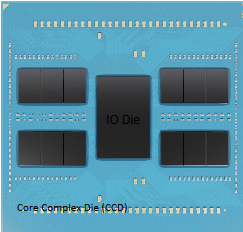

Схема процессора

Процессоры AMD серии EPYC 9004 объединяют вычислительные ядра, контроллеры памяти, контроллеры ввода-вывода, функции надежности, доступности и удобства обслуживания (RAS), а также безопасность в рамках интегрированной системы на кристалле (SoC). Процессор EPYC 9004 сохраняет зарекомендовавшую себя многочиповую модульную архитектуру (MCM) предыдущих успешных процессоров AMD EPYC, в то же время улучшая компоненты SoC.

SoC содержит матрицу core complex (CCD), которая включает в себя модули core complex (CCX), содержащие ядра на базе Zen 4. Эти ПЗС-матрицы окружены кристаллом высокоскоростного ввода-вывода (I/O) и подключены через infinity fabric. В этом разделе будет подробно описан каждый из этих компонентов.

Ядро Zen 4

«Zen 4» — это последняя версия микроархитектуры AMD Zen, которая обеспечивает работу ядер процессоров EPYC 9004. Эти ядра разработаны таким образом, чтобы обеспечивать высокую производительность и КПД, что делает их идеальными для рабочих нагрузок в центрах обработки данных. Архитектура «Zen 4» включает в себя ряд улучшений по сравнению с предыдущими версиями, таких как увеличение количества ядер, увеличение объема кэш-памяти и повышение энергоэффективности. Процессоры AMD серии EPYC 9004 основаны на вычислительном ядре «Zen 4», которое изготавливается по 5-нм технологическому процессу. Ядро «Zen 4» обеспечивает увеличение количества команд на цикл (IPC) и частоты выполнения по сравнению с предыдущими поколениями ядер «Zen». Каждое ядро включает в себя кэш-память L2 большего размера с улучшенной эффективностью кэширования по сравнению с предыдущим поколением.

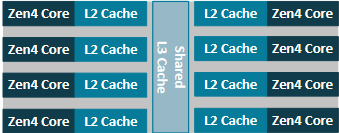

Каждое ядро «Zen 4» имеет до 32 КБАЙТ 8-стороннего I-кэша и до 32 КБАЙТ 8-стороннего D-кэша. Оно также имеет частный унифицированный (инструкции/данные) L2-кэш объемом до 1 МБ. Ядро поддерживает одновременную многопоточность (SMT), позволяя двум отдельным аппаратным потокам работать независимо и совместно использовать кэш L2 ядра.

На рисунке 2-2 показан комплекс ядер (CCX), в котором до восьми ядер на базе Zen 4 совместно используют кэш L3 или последнего уровня (LLC). Включение SMT позволяет одному CCX поддерживать до 16 параллельных аппаратных потоков. Кэш L2 ядра Zen4

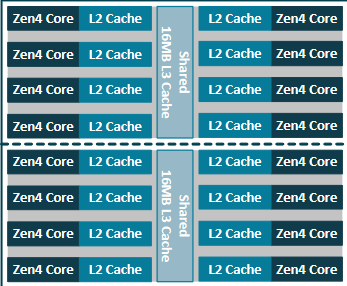

Комплексные матрицы ядра (CCD)

Матрица Core Complex (CCD) в процессоре AMD EPYC серии 9xx4 может содержать один или два модуля CCX, в зависимости от модели (91xx-96xx «Genoa» или 97xx «Bergamo»), как показано на рисунке 2-5. Каждый CCD-матрица в процессоре AMD EPYC 97xx содержит два CCX-матрицы.

Вы можете настроить количество активных ядер в BIOS, уменьшив количество ядер на L3 или отключив их. Такой подход уменьшает эффективный размер кэша на ядро, но увеличивает количество ядер, совместно использующих кэш.• Уменьшите количество активных ПЗС-накопителей, сохранив при этом количество ядер на ПЗС-накопитель постоянным. Такой подход сохраняет преимущества совместного использования кэша между ядрами при сохранении того же соотношения кэш-памяти на ядро.

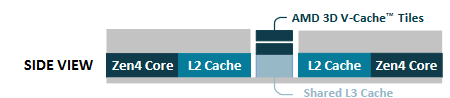

Технология AMD 3D V-Cache

Процессоры AMD EPYC серии 9xx4X оснащены технологией AMD 3D V-Cache, которая позволяет компании 9xx добиться более эффективной интеграции чиплетов. Архитектура AMD 3D chiplet обеспечивает вертикальное расположение элементов кэш-памяти L3, обеспечивая до 96 МБ кэш-памяти L3 на кристалле (и до 1 ГБ кэш-памяти L3 на сокете), сохраняя при этом совместимость со всеми моделями процессоров AMD EPYC серии 9004. Процессоры AMD серии EPYC 9004 с технологией AMD 3D V-Cache используют передовую в отрасли логическую схему, основанную на гибридном соединении «чип на пластине» без зазоров, что обеспечивает более чем в 200 раз большую плотность межсоединений по сравнению с современными 2D-технологиями и более чем в 15 раз большую плотность межсоединений по сравнению с другими 3D-технологиями, которые используются в настоящее время. используйте припойные выступы. Это приводит к снижению задержки, увеличению пропускной способности и повышению энергетической и тепловой эффективности.

В процессорах AMD серии EPYC 9004 максимальный общий объем кэш-памяти L3 на CCD составляет 32 МБ или 96 МБ. В таблице показан объем кэш-памяти L3 для каждой модели процессора.

Разные OPN могут иметь разное количество ядер в CCX, но для любой заданной части все CCX будут содержать одинаковое количество ядер.

Источник: royal-computers.ru

12 комментариев

Добавить комментарий

окружают кристалл

Epyc

Ну так в оригинале же скорее всего «CCD», но робот перевёл CCD как ПЗС — А автор вообще походу не шибко в теме, да и с орфографией тоже, много проблем.

Это не вид сверху, это схема.

О, а тут уже таблица. Хотя картинка почти такая же.

Простите, какой компании?

Автор — ты не автор, ты плохой пользователь системы автоматического перевода. Плохой системы автоматического перевода.

Надеялся наткнуться на упоминание источника на зарубежном ресурсе, чтобы его прогнать через тот-же гугл транслейт. Но ссылка на фирму.

Открывая статью — думал, ну вот же, тема для IXBT, но нет… IXBT уже не тот, какой-то «за рулём», с «работницей» наполовину. Даже не «моделист-конструктор».

Оверклокерсы скатились в жёстчайшую пропаганду. Эти скатились в бытовуху и автопром. Ситилинк и ДНС торгует всем подряд, скоро навоз продавать будут. Хрень какая-то.

Добавить комментарий