На начавшем работу Microprocessor Forum, AMD рассказала детали о новом поколении своих 64-битных процессоров, носящих условное название Hammer.

По замыслу AMD, как поведал на форуме Фред Вебер (Fred Weber), вице-президент и CTO компании, архитектура Hammer, разработанная для расширения присутствия AMD в серверном секторе, в двух-, четырех– и восьмипроцессорных системах, тем не менее, обязательно появится в качестве версий для настольных ПК и ноутбуков. Идеология Hammer – по-прежнему неизменна: сохраняя полную совместимость с существующим 32-битном ПО, обеспечить плавный, наименее болезненный переход на 64-битные вычисления. Как ни странно, но тут же, в рассказе о новом семействе Hammer, была упомянута новая PR-идеология AMD - True Performance Initiative, и было подчеркнуто, что архитектура Hammer также будет подаваться с QuantiSpeed, то есть, с новоявленными PR-рейтингами.

О самой архитектуре Hammer: как было подчеркнуто, компания намерена обеспечить исполнение и 32-, и 64-битного кода с максимальной эффективностью, причем, без потерь производительности в 32-битных приложениях. Конечно, была упомянута и HyperTransport, но, по сути, в официальном пресс-релизе – больше, конечно, воды, и за деталями пришлось обратиться к 47-страничному документу, проливающему некоторый свет на новые процессоры.

Главная, на мой взгляд, идея программной модели Hammer: AMD подчеркивает, что ее новый набор команд x86-64 - прямой наследник набора x86, лишь дополняющий и расширяющий его. 48-битное адресное пространство, 40-битное физическое, восемь новых целочисленных регистров, полная поддержка набора инструкций SSE/SSE2, и так далее. Модель работы с кодом, как заявлено, должна будет впитать в себя лучшее из CISC и RISC моделей, в частности, основываясь на CISC модели, будет использоваться обработка RISC-образных команд с помощью бинарного интерфейса (ABI, Application Binary Interface).

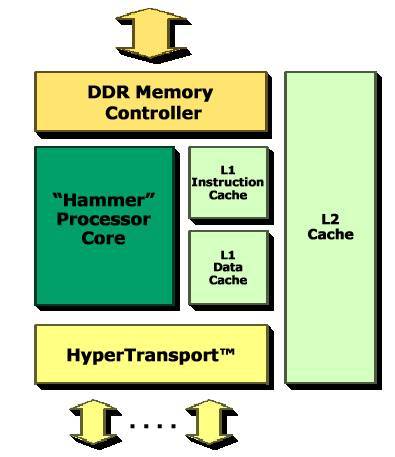

Вот так выглядит сама, скажем так, идеология ядра Hammer

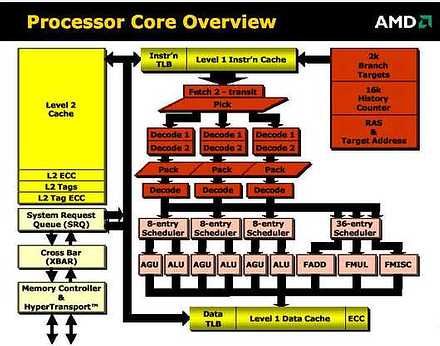

А это – более детальные подробности:

В рамках новости, конечно, всех любопытных деталей не передать, но хотелось бы еще упомянуть о решении использовать интегрированный контроллер DDR памяти, что позволит, например, в восьмипроцессорных системах довести количество памяти до 128 Гб (в сумме, 64 разъема DIMM).

В рамках MPF никаких заявлений о сдвигах сроков выпуска процессоров нового семейства не прозвучало. Похоже, пока будем ориентировался на даты, представленные в выложенном позавчера роадмэпе.