В самых первых строках мы хотели бы совершенно чётко обозначить целевую аудиторию этой статьи: это ни в коем случае не практичные люди. Полученные из этого материала сведения наверняка не увеличат качество вашей жизни, размер оклада или быстродействие компьютера — да и вообще никакого влияния на вашу жизнь не окажут, даже похвастаться перед друзьями и коллегами будет нечем. Но если вы интересуетесь x86-архитектурой и процессорами на её основе так же искренне и беззаветно, как интересуемся этим мы, авторы — то мы постараемся, чтобы в процессе чтения вам было, как минимум… нескучно. ;)

Преамбула

В задаче создания общей классификации x86-процессоров (далее по тексту мы для краткости будем их называть просто «процессорами» или ЦП), самым важным является ответ на вопрос о том, зачем нам вообще нужна эта классификация. Ведь несколько десятков лет без неё жили, а тут вдруг понадобилась? И вообще, зачем в принципе нужны эти классификации? Отбросим клеветнические обвинения в том, что классификации нужны, чтобы было о чём писать, когда больше не о чем. На самом деле нужда в них возникает, когда мы настолько заблудились в эмпирически полученных знаниях в определённой области, что уже требуется их упорядочить. Для чего требуется соблюдение по крайней мере трёх условий:

- Знания должны быть как-то формализуемы, иначе нечего упорядочивать.

- Знания должны поддаваться упорядочиванию, иначе задача нерешаема.

- Знаний должно быть достаточно много, чтобы упорядочивание имело смысл.

Очевидно, что пунктам 1 и 3 наши знания о x86-процессорах вполне соответствуют: они имеют формализуемые общие признаки, и самих признаков (а в ещё большей степени — собственно устройств) с 1978 года появилось вполне достаточно, чтобы возникло законное желание разобраться во всём этом бардаке. А вот имеет ли положительный ответ вопрос номер 2?.. Честно говоря, авторы не уверены в этом до конца даже по окончании написания статьи. Однако уж слишком много забавных мыслей появилось в процессе поиска ответа на этот вопрос, чтобы просто так отставить их в сторону. Решив заразить своей идеей читателей, мы предлагаем вам своего рода «статью-вопрос»: она начинается формулировкой проблемы, продолжается нашими рассуждениями и заканчивается неким промежуточным итогом. Является ли он окончательным, или же мы уплыли ещё дальше от истины, чем были в начале — не знаем. Потому с удовольствием выслушаем здравую критику.

Есть одна интересная гипотеза: всё ниженаписанное на самом деле является робкой попыткой понять, как развивалась архитектура x86. А задача разработки классификации является лишь формальным оправданием сего. ;)

Общие признаки процессоров

Естественно, классификация должна на чём-то базироваться. Для этого нам понадобилось сначала выделить у ЦП некие общие признаки, которые бы, с одной стороны, «пронизывали» всё семейство насквозь, а с другой — отражали наиболее весомые вехи в развитии процессоров архитектуры x86. Здесь мы кратко перечислим эти признаки в том виде, в котором этот список был утверждён нами на момент окончания работы. Подразумевается, что чем ближе процессор находится к начальному этапу развития — тем меньшим количеством признаков он обладает; современные же ЦП обладают ими в полном объёме.

- Поддержка выполнения кода процессора i8086. Ну да, а что ещё взять в качестве первого и основного признака ЦП архитектуры x86? В принципе, подошло бы «наличие цифры 86 в конце названия», но хитрые японцы из фирмы NEC выпустили процессоры серии V, где это правило не соблюдается.

- Поддержка виртуальной памяти и многозадачности. Очевидно, что появление этих свойств у процессоров семейства x86 было одним из ключевых этапов в развитии архитектуры в целом.

- 32-разрядность. Несмотря на то, что де-факто она появилась в архитектуре x86 практически одновременно с поддержкой виртуальной памяти и многозадачности, мы всё же выделили данный признак в отдельный.

- Встроенный FPU. Впервые появившись в процессорах i486DX, впоследствии внутренний FPU очень быстро стал неотъемлемой частью практически всех x86-процессоров, т. к. процессоры с ним получали существенное преимущество в скорости выполнения операций с плавающей запятой.

- Встроенный кэш L1. Строго говоря, на момент своего появления он ещё не носил названия «L1», т. к. уровень был единственный. Это новшество существенно увеличивает скорость исполнения почти любого кода.

- RISC-подобное ядро. Это крупнейшее достижение процессоростроения объединило в себе коня RISC (быстро, но не сильно-то удобно для программистов) и трепетную лань CISC (не так быстро, но в коде красота). Такие гибриды со всеми их конвейерами и микрооперациями начали новую эпоху в развитии ЦП.

- Умножитель частоты ядра. Исполнительный конвейер позволил резко нарастить частоты внутренностей ЦП, так что его окружение уже не успевало за ним. Потому процессор стал работать в кратное число раз (а после — в полуцелое) быстрее, чем всё остальное благодаря встроенному умножителю частоты.

- Конвейеризованный FPU. Фактически, это RISC-подобная организация именно FPU. Пункт выше прежде всего касался целочисленной части ЦП.

- Суперскалярность (с IPC=2). Параметр IPC (кол-во команд за такт) нам уже знаком по теоретическим статьям. А переход на суперскалярность, как ни крути, существенно усложняет ЦП, и (теоретически) поднимает его производительность.

- Суперскалярность с IPC=3. Дальнейшее развитие концепции суперскалярности, сопровождавшееся существенным усложнением ядра ЦП.

- OoO. Технология внеочередного исполнения команд (Out-of-Order [Execution]) явилась достаточно очевидным нововведением для конвейерных процессоров (а без конвейера невозможна и суперскалярность, так что он к этому времени был у всех).

- Встроенный кэш L2. Был на плате, стал внутри корпуса. Но не обязательно на самом чипе — см. исключения ниже.

- Поддержка целочисленных SIMD-инструкций. Из всей парадигмы «одна команда — много данных» в данном случае имеется ввиду технология MMX. Вообще-то, были и дополнения к этим командам, но об этом чуть позже. Уже MMX хватило, чтобы значительно ускорить оптимизированные программы.

- Вещественные SIMD-наборы. Аналогичное предыдущему улучшение, позволившее разогнать вещественную производительность. Правда, разных наборов так много, что потом придётся этот пункт несколько пересмотреть…

- Суперскалярность с IPC=4. Ещё один этап развития архитектуры и усложнения ядра.

- 64-разрядность. Мельчают признаки, да?… А что делать, не радуют производители новинками, приходится перебиваться, чем есть — расширение виртуальной адресации, удвоение числа регистров и всякие малозначимые мелочи.

- Встроенный контроллер памяти. Олицетворяет тенденцию дальнейшей интеграции в ЦП того, что ранее было на материнской плате.

- Многоядерность. Кардинально ничего нового, но степень интеграции ЦП (как минимум на уровне его корпуса) повысилась, и теперь то, что мы называем процессор, потенциально стало в кратное число раз быстрее.

- Встроенный кэш L3. А это олицетворяет скорее проблемы архитектуры, чем её достижения. Но и в таком контексте это вполне определяющий признак.

- Технология TurboBoost. Тут на микроархитектурном уровне нового совсем с гулькин нос. TurboBoost является просто легализованным и автоматизированным частотным разгоном. Но поскольку она штатно включена и присутствует уже в немалом числе ЦП, включим её и мы, но не сразу :)

Вот на этих 18-20 ключевых признаках (смотря как считать…) мы и намеревались построить нашу будущую классификацию. И начали строить…

Попытка №1

Конечно же, нам ещё в детстве рассказали, что нормальные герои всегда идут в обход. Однако задача на первых порах казалась такой простой, что мы сразу решили опробовать самый «лобовой» способ: создание классификации с опорой на основные поколения процессоров Intel (ну и, быть может, с какими-то небольшими отклонениями и реверансами в сторону других компаний). Пока поклонники этих самых «других» не начали кричать «Позор!», поясним, почему был столь велик соблазн. Дело в том, что если посмотреть на историю архитектуры x86, то период от i8086 до i486 — это как минимум половина этой истории, причём как бы не бОльшая. И характеризуется эта половина прежде всего тем, что в те времена не драл у Intel только ленивый, причём некоторые драли всё целиком. (Не будем останавливаться на нюансах лицензирования, кто кому за что заплатил или нет — с точки зрения инженера-разработчика это всё равно называется «драли», независимо от денежных и юридических деталей.) Т. е. по крайней мере по 486-й процессор включительно классификация поколений от Intel действительно отражала основной вектор развития архитектуры в целом, а дальше — будем надеяться на принцип «авось кривая вывезет». Поэтому для начала был взят модельный ряд ЦП Intel, и на его основе написан список ключевых признаков каждого поколения, примерно отражающий время их появления именно в процессорах этой компании. Первоначальный список признаков поколений был такой (номера в списке — это поколения и есть):

- Поддержка выполнения кода процессора i8086.

- Поддержка виртуальной памяти, многозадачности и 32-битности.

- Встроенный FPU, L1-кэш, RISC-подобное ядро, множитель.

- Конвейеризованный FPU, IPC=2, целочисленные SIMD.

- IPC=3, OoO, L2 кэш, расширенные SIMD.

- IPC=4, многоядерность, 64-битность.

- Контроллер памяти, L3-кэш.

Разумеется, у кого-то сразу возникнет желание раскритиковать нас в пух и прах, но повторимся: в целом, развитие линейки процессоров Intel этот список отражает действительно неплохо (что мы сейчас и продемонстрируем), а основная идея пока что заключается в том, что нам удастся притянуть за уши и все остальные процессоры, причём достаточно малой кровью. Далее представлена классификация №1 в её окончательном виде — тут и нумерация поколений, и список признаков успели существенно поменяться. Позже мы объясним, зачем это сделано, и почему не помогло. :)

Классификация первая, «проинтеловская»

Описание поколений

- 1 поколение — способность исполнять код i8086 (IA16).

- 1+ поколение — частичная паралеллизация исполнения команд, специализация ФУ.

- 2 поколение — поддержка виртуальной памяти, многозадачности и 32-битности (IA32).

- 2+ поколение — L1-кэш.

- 3 поколение — встроенный FPU, исполнительный конвейер (не обязательно для RISC-подобных микроопераций).

- 3+ поколение — умножитель частоты ядра.

- 4 поколение — IPC>=2, специализация L1.

- 4+ поколение — SIMD: 4/2/1-байтовые целые (обозначено как 4i).

- 5 поколение — конвейеризованный FPU, OoO, L2-кэш.

- 5+ поколение — IPC>=3, SIMD: вещественные одинарной (SP) и двойной (DP) точности, 8/4/2/1-байтовые целые (SP+4i и DP+8i).

- 6 поколение — многоядерность, 64-битность (x86-64).

- 6+ поколение — встроенный контроллер памяти, L3-кэш.

Правила формирования поколений

Процессор относится к определённому поколению в том случае, если у него присутствуют все признаки этого и всех предыдущих поколений. Правило образования исключений: процессор может быть продвинут вперёд на полпоколения, даже если у него отсутствует требуемая функциональность, но присутствует другая функциональность более позднего поколения.

Практическое воплощение

| ЦП | Поколение | FPU: Внешний, (Не)Конвейерный | Множитель | SIMD | Конвейеры (IPC) | OoO, HT | Многоядерность | Макс. уровень кэша в ЦП | Контроллер памяти | Виртуальная память, многозадачность | Разрядность адресации 1 |

| …86/88 (все) | 1 | В | − | − | 0 | − | − | 0 | − | − | 20 |

| …286 (все) | 1+ | В | − | − | 0 | − | − | 0 | − | − 2 | 24 |

| …386… (кроме указанных ниже) | 2 | В | − | − | 0 | − | − | 0 | − | + | 32 |

| IBM 386SLC, 486DLC/SLC; Chips&Technologies 38605DX | 2+ | В | − | − | 0 | − | − | 1 | − | + | 32 |

| IBM 486DLC2/SLC2 | 2+ | В | + | − | 0 | − | − | 1 | − | + | 32 |

| Intel i80486SX; AMD Am486SX; IBM 486BLX; Cyrix Cx486SR…, Cx486D/S…; Texas Instruments TI486SX…; UMC U5S… | 2+ | В | − | − | 1 | − | − | 1 | − | + | 32 |

| …486DX… (остальные, без цифры); UMC U5D… | 3 | НК | − | − | 1 | − | − | 1 | − | + | 32 |

| Intel RapidCAD | 2+ | НК | − | − | 1 | − | − | 0 | − | + | 32 |

| …486DX…/BLX…/DLC… (с цифрой); AMD Am5x86 X5 | 3+ | НК 3 | + | − | 1 | − | − | 1 | − | + | 32 |

| Intel Pentium | 4 | К | + | − | 2 | − | − | 1 | − | + | 32 |

| Intel Pentium MMX | 4+ | К | + | 4i | 2 | − | − | 1 | − | + | 32 |

| Intel Pentium Pro | 4+ 6 | К | + | − | 3 | OoO | − | 2 | − | + | 36 |

| Intel Pentium II | 5 | К | + | 4i | 3 | OoO | − | 2 | − | + | 36 |

| Intel Pentium III | 5+ | К | + | SP+4i | 3 | OoO | − | 2 | − | + | 36 |

| Intel Pentium 4/M, Core | 5+ | К | + | DP+8i | 3 | OoO | − | 2 | − | + | 36 |

| Intel Pentium D/EE | 6 | К | + | DP+8i | 3 | обе | + | 2 | − | + | 64 |

| Intel Core 2 | 6 | К | + | DP+8i | 4+1 | OoO | + | 2 | − | + | 64 |

| Intel Atom | 5+ 7 | К | + | DP+8i | 2 | HT | + | 2 | − | + | 64 |

| Intel Core i7 | 6+ | К | + | DP+8i | 4+1 | обе | + | 3 | + | + | 64 |

| IDT WinChip C6(+) | 4+ | НК | + | 4i | 1 | − | − | 1 | − | + | 32 |

| IDT WinChip 2 | 4+ | К | + | SP+4i | 1~2 | − | − | 1 | − | + | 32 |

| AMD K5, 5k86 | 4+ | К | + | − | 2~4 | OoO | − | 1 | − | + | 32 |

| AMD K6 | 4+ | НК | + | 4i | 2 | OoO | − | 1 | − | + | 36 |

| AMD K6-2 | 4+ | НК | + | SP+4i | 2 | OoO | − | 1 | − | + | 36 |

| K6-2+, K6-III | 5 8 | НК | + | SP+4i | 2 | OoO | − | 2 | − | + | 36 |

| AMD Athlon (K7), XP | 5+ | К | + | SP+4i | 3 | OoO | − | 2 | − | + | 36 |

| AMD Athlon 64 (K8) | 6 | К | + | DP+8i | 3 | OoO | + | 2 | + | + | 64 |

| AMD Phenom (K10) | 6+ | К | + | DP+8i | 3 | OoO | + | 3 | + | + | 64 |

| Cyrix 5x86/M1sc; IBM 5x86C | 3 | НК | + | − | 1 | − | − | 1 | − | + | 32 |

| Cyrix 6x86/M1(R) | 4 | НК | + | − | 2 | OoO | − | 1 4 | − | + | 32 |

| Cyrix 6x86MX (M II) | 4+ | НК | + | 4i | 2 | OoO | − | 1 4 | − | + | 32 |

| VIA C3 | 5 9 | К | + | SP+4i | 1 | − | − | 2 | − | + | 32 |

| VIA C7 | 5 9 | К | + | DP+8i | 1 | − | − | 2 | − | + | 32 |

| VIA Nano | 5+ | К | + | DP+8i | 3 | OoO | − | 2 | − | + | 64 |

| Rise mP6 | 4+ | К | + | 4i | 2~3 | − | − | 1 | − | + | 32 |

| Transmeta Crusoe | 5+ 10 | К | + | 4i | 4 | 5 | − | 2 | + | + | 32 |

| Transmeta Efficeon | 5+ | К | + | DP+8i | 8 | 5 | − | 2 | + | + | 32 |

| NexGen Nx586 | 3+ 11 | В | − | − | 1 | OoO | − | 1 | − | + | 32 |

| NexGen Nx686 | 4+ | НК | + | 4i | 2 | OoO | − | 1 | − | + | 32 |

1 — реальная или виртуальная (при наличии виртуальной памяти) ↑

2 — неудачная реализация, практически не использовалась ↑

3 — кроме редких моделей …486S2…/SX(L)2/DLC2/SLC2/DR…/SR… без сопроцессора ↑

4 — общий кэш L1 ↑

5 — исполняется «сверхдлинное машинное слово» (VLIW), преобразованное из кода x86 с перетасовкой команд при формировании (их число указано в столбце конвейеров) ↑

6 — формально 4 (отсутствует поддержка SIMD), +0,5 добавлено за признак 5-го поколения — L2-кэш ↑

7 — формально 4+ (отсутствует OoO), +1 добавлено за 2 признака 6-го поколения — многоядерность и 64-разрядность ↑

8 — формально 4+ (отсутствует конвейеризованный FPU), +0,5 добавлено за признак поколения 5+ — SIMD SP+4i ↑

9 — формально 4+ (отсутствует OoO), +0,5 добавлено за признак поколения 5+ — SIMD SP+4i ↑

10 — формально 5 (отсутствует поддержка SIMD SP+4i), +0,5 добавлено за признак поколения 6+ — контроллер памяти ↑

11 — формально 2+ (отсутствует FPU), +1 добавлено за признак 4-го поколения (IPC>=2) и признак 5-го поколения (OoO) ↑

Критический самоанализ

Заголовок «Попытка №1» подразумевает, что «у нас с собой было» гораздо больше — и действительно, предположение о вывозящей кривой оказалось крайне неверным, и даже попытки хоть до i486 опереться только на Intel — тоже не совсем успешными. Классификация стала трещать по швам на первых же строчках, т. к. исходя из первоначального списка признаков получалось, что все процессоры до 386-го относятся к одному и тому же поколению.

Между прочим, один из авторов даже был за то, чтобы так всё и оставить, мотивируя это простым доводом — де-факто, так оно и было: и i80186 (если кому повезло наткнуться на эту редкую в ПК птицу), и даже i80286 подавляющим большинством использовались просто как «быстрые XT-шки», т. е. как более скоростной аналог i8086 или i8088. Даже частичная реализация в i80286 привычного нам по более поздним CPU «защищённого режима» эту тенденцию переломить не смогла — реализован он был, мягко говоря, «неаккуратненько», так что охотников им пользоваться в требуемом количестве так и не нашлось. Кстати: Microsoft Windows, начиная с версий 3.11, и вовсе считает, что никакого защищённого режима у 286-го процессора нет (а у 386-го — уже есть).

Ладно, образовали специально для 286-го промежуточное поколение 1+, мотивируя тем, что кроме как бы защищённого как бы режима там имелась и первая попытка конвейеризации операций, реально приводившая к серьёзному увеличению производительности. В общем: «Пусть будет поколение 1+, потому что всё-таки сильно быстрее стал». Обратите внимание: уже здесь в обсуждении классификации впервые прозвучал аргумент быстродействия.

С 386-ми и 486-ми тоже всё непросто. По таблице видно, что некоторые ЦП «альтернативных» производителей представляли собой попытки сделать быстрый 386-й и назвать его 486-м, или же наоборот, сделать довольно медленный и сильно урезанный 486-й, но называть его… ага, тоже 486-м. :) С этими мелкими нескладушками мы расправлялись, походя множа подклассы и перетасовывая по ним признаки — после чего стало окончательно ясно, что без «промежуточных» поколений нам обойтись не удастся уже ни на каком этапе.

Но как только мы наконец-то вышли на широкий простор условно второй половины нашей истории, тут нас поджидало ещё больше интересного. Потому что начиная с Pentium (того самого, «первого»), компания Intel перестала продавать и раздавать лицензии, и все «особо альтернативные» фирмы были вынуждены либо завязывать с рынком x86 вообще, либо начинать разрабатывать что-то своё. Посмотрев на сравнение функциональности процессоров тех времён, мы сразу же вспомнили и мартышкин концерт, и лебедя, щуку и рака, и другие известные произведения великого русского баснописца. Во-первых, согласно формальным признакам, Pentium Pro из-за отсутствия MMX попадал в ту же категорию, что и Pentium (да, серверным процессорам не особенно нужен MMX, но не вводить же из-за этого общий признак «серверность»?). Во-вторых, Intel Atom из-за отутствия Out-of-Order Execution вообще попадал в то же поколение, что и Pentium MMX. И это уже на платформе Intel! Ну а с продукцией «коллег по цеху» ещё интереснее — и AMD K6-2+/III, и VIA C3/C7 и Transmeta Crusoe попадали, согласно утверждённым формальным признакам, совершенно не в те поколения, которые наш здравый смысл был бы согласен принять без существенных возражений. А тут ещё маячит NexGen Nx586, который по формальным признакам вроде как поколение 2+, но у него есть OoO, что является признаком 5-го поколения!

Вооружившись терпением, пришлось придумывать различные отмазки оправдания для переноса процессоров из того поколения, к которому они по формальным признакам должны были относиться, в то, которое диктовал тот самый авторский здравый смысл (варианты этих отмазок оправданий можно наблюдать в виде примечаний к таблице). Дойдя до конца и перераспределив все ЦП по поколениям, посмотрели мы на дело рук своих… и ужаснулись. Потому что на 40 строк таблицы у нас получилось 11 исключений! И стало понятно, что «так жить нельзя»…

Попытка №2

Так как желание получить нечто стройное и логичное достаточно недорогой ценой ещё не испарилось, мы предприняли вторую попытку. Суть сделанного предположения такова: ладно, процессоры разных производителей упорно не желают чётко придерживаться раз и навсегда утверждённой последовательности появления определённых признаков. А что если «размазать» ключевые вехи, сделав их менее чёткими?

Вооружившись тем же списком ключевых признаков (жалко было выбрасывать — так долго делали…), мы принялись перетасовывать признаки по поколениям и менять формулировки правил формирования поколений. Цель ясна: признаки остаются теми же, разнесение их по поколениям можно менять, формулировку правил тоже, но ни одного исключения в таблице быть не должно. А главное — глядя всё это, авторский здравый смысл должен молчать, в крайнем случае — тихонько бурчать что-то нечленораздельное в дальних закоулках сознания. И у нас даже почти получилось! Давайте взглянем на это чудо.

Классификация вторая, «интернационально-вольнодумная»

Описание поколений

- 1 поколение — IA16.

- 2 поколение — поддержка виртуальной памяти, IA32, L1.

- 3 поколение — FPU, конвейер, множитель.

- 4 поколение — IPC>=2, целочисленные SIMD, конвейерный FPU.

- 5 поколение — OoO, L2, IPC>=3, вещественные SIMD.

- 6 поколение — многоядерность, x86-64, контроллер памяти, L3.

Правила формирования поколений

Процессор может быть отнесён к определённому поколению, если у него есть хотя бы N-1 признаков этого поколения (т. е. на единицу меньше их числа из списка выше), причём есть ли у процессора все признаки предыдущих поколений — не важно.

Практическое воплощение

| ЦП | Поколение | FPU: Внешний, (Не)Конвейерный | Множитель | SIMD | Конвейеры (IPC) | OoO, HT | Многоядерность | Макс. уровень кэша в ЦП | Контроллер памяти | Виртуальная память, многозадачность | Разрядность адресации 1 |

| …86/88 (все) | 1 | В | − | − | 0 | − | − | 0 | − | − | 20 |

| …286 (все) | 1 | В | − | − | 0 | − | − | 0 | − | − 2 | 24 |

| …386… (кроме указанных ниже) | 2 | В | − | − | 0 | − | − | 0 | − | + | 32 |

| IBM 386SLC, 486DLC/SLC; Chips&Technologies 38605DX | 2 | В | − | − | 0 | − | − | 1 | − | + | 32 |

| IBM 486DLC2/SLC2 | 2 | В | + | − | 0 | − | − | 1 | − | + | 32 |

| Intel i80486SX; AMD Am486SX; IBM 486BLX; Cyrix Cx486SR…, Cx486D/S…; Texas Instruments TI486SX…; UMC U5S… | 2 | В | − | − | 1 | − | − | 1 | − | + | 32 |

| …486DX… (остальные, без цифры); UMC U5D… | 3 | НК | − | − | 1 | − | − | 1 | − | + | 32 |

| Intel RapidCAD | 3 | НК | − | − | 1 | − | − | 0 | − | + | 32 |

| …486DX…/BLX…/DLC… (с цифрой); AMD Am5x86 X5 | 3 | НК 3 | + | − | 1 | − | − | 1 | − | + | 32 |

| Intel Pentium | 4 | К | + | − | 2 | − | − | 1 | − | + | 32 |

| Intel Pentium MMX | 4 | К | + | 4i | 2 | − | − | 1 | − | + | 32 |

| Intel Pentium Pro | 5 | К | + | − | 3 | OoO | − | 2 | − | + | 36 |

| Intel Pentium II | 5 | К | + | 4i | 3 | OoO | − | 2 | − | + | 36 |

| Intel Pentium III | 5 | К | + | SP+4i | 3 | OoO | − | 2 | − | + | 36 |

| Intel Pentium 4/M, Core | 5 | К | + | DP+8i | 3 | OoO | − | 2 | − | + | 36 |

| Intel Pentium D/EE | 6 | К | + | DP+8i | 3 | обе | + | 2 | − | + | 64 |

| Intel Core 2 | 6 | К | + | DP+8i | 4+1 | OoO | + | 2 | − | + | 64 |

| Intel Atom | 6 | К | + | DP+8i | 2 | HT | + | 2 | − | + | 64 |

| Intel Core i7 | 6 | К | + | DP+8i | 4+1 | обе | + | 3 | + | + | 64 |

| IDT WinChip C6(+) | 3 | НК | + | 4i | 1 | − | − | 1 | − | + | 32 |

| IDT WinChip 2 | 4 | К | + | SP+4i | 1~2 | − | − | 1 | − | + | 32 |

| AMD K5, 5k86 | 4 | К | + | − | 2~4 | OoO | − | 1 | − | + | 32 |

| AMD K6 | 4 | НК | + | 4i | 2 | OoO | − | 1 | − | + | 36 |

| AMD K6-2 | 4 | НК | + | SP+4i | 2 | OoO | − | 1 | − | + | 36 |

| K6-2+, K6-III | 4 | НК | + | SP+4i | 2 | OoO | − | 2 | − | + | 36 |

| AMD Athlon (K7), XP | 5 | К | + | SP+4i | 3 | OoO | − | 2 | − | + | 36 |

| AMD Athlon 64 (K8) | 6 | К | + | DP+8i | 3 | OoO | + | 2 | + | + | 64 |

| AMD Phenom (K10) | 6 | К | + | DP+8i | 3 | OoO | + | 3 | + | + | 64 |

| Cyrix 5x86/M1sc; IBM 5x86C | 3 | НК | + | − | 1 | − | − | 1 | − | + | 32 |

| Cyrix 6x86/M1(R) | 3 | НК | + | − | 2 | OoO | − | 1 4 | − | + | 32 |

| Cyrix 6x86MX (M II) | 4 | НК | + | 4i | 2 | OoO | − | 1 4 | − | + | 32 |

| VIA C3 | 4 | К | + | SP+4i | 1 | − | − | 2 | − | + | 32 |

| VIA C7 | 4 | К | + | DP+8i | 1 | − | − | 2 | − | + | 32 |

| VIA Nano | 5 | К | + | DP+8i | 3 | OoO | − | 2 | − | + | 64 |

| Rise mP6 | 4 | К | + | 4i | 2~3 | − | − | 1 | − | + | 32 |

| Transmeta Crusoe | 5 | К | + | 4i | 4 | 5 | − | 2 | + | + | 32 |

| Transmeta Efficeon | 5 | К | + | DP+8i | 8 | 5 | − | 2 | + | + | 32 |

| NexGen Nx586 | 2 | В | − | − | 1 | OoO | − | 1 | − | + | 32 |

| NexGen Nx686 | 3 | НК | + | 4i | 2 | OoO | − | 1 | − | + | 32 |

1 — реальная или виртуальная (при наличии виртуальной памяти) ↑

2 — неудачная реализация, практически не использовалась ↑

3 — кроме редких моделей …486S2…/SX(L)2/DLC2/SLC2/DR…/SR… без сопроцессора ↑

4 — общий кэш L1 ↑

5 — исполняется «сверхдлинное машинное слово» (VLIW), преобразованное из кода x86 с перетасовкой команд при формировании (их число указано в столбце конвейеров) ↑

Критический самоанализ

Как вы помните (по крайней мере, мы на это надеемся), классификация №1 была нами забракована по причине того, что в ней было слишком много «введённых вручную» исключений с не всегда вразумительными объяснениями. Приказ «Ни шагу назад!» «Ни одного исключения!» оказался выполнен, но… похоже, слишком дорогой ценой. Да, ни одного исключения не наблюдается. Но может ли такой принцип отбора гордо претендовать на звание классификации?

Во-первых, признаки отбора изначально достаточно сильно размыты: из указанного N количества признаков процессору разрешено не иметь любой один. Это сколько же вариантов различных комбинаций признаков у нас будет относится к одному поколению? Во-вторых — опять-таки в погоне за «исключением исключений» мы согласились принять, что признаками предыдущих поколений следующее может и не обладать. А значит практически в каждом поколении образовалось большое число ЦП, которые либо не имеют одного из признаков предыдущих поколений, либо имеют некоторые признаки следующих. В общем, все формальности вроде бы соблюдены, кроме одной небольшой детали — осмысленности результатов проведённой работы. Классификация вроде бы есть, но если взглянуть на неё пристально, то обнаруживается, что единственная цель, для которой она пригодна — чтобы отчитаться о том, что мы её таки придумали. Но мы же её писали всё-таки не для этого! ;)

Попытка №3

Выставленная на показ в форуме вторая версия классификации вызвала характерную реакцию типа «что это было?», посему мы решили снова начать всё с нуля, т. к. до сих пор полемика была на уровне «нужен-не-нужен такой-то признак» и «5-е или 6-е поколение у такого-то ЦП». Поскольку x86-процессоры, как оказалось, сильно разные и часто не имеют ожидаемых элементов, нужно было найти то, что точно есть у всех. После недолгих поисков, такая штука нашлась — производительность. Методов её увеличения придумано много, реализованы почти все, и каждый даёт некоторую долю в общий вклад. Осталось только оценить эту долю, посчитать скорость, сделать ранжир и рассчитаться по порядку. Тем более, что уже в первой классификации были намёки, что всё к этому и идёт.

В таблице ниже указаны коэффициенты ускорения для каждой технологии, блока и метода, которыми в изобилии снабжён современный ЦП. Причём указано ускорение, достигнутое в тех ЦП, где новинка появилась, но только в пределах одного поколения (хотя мы ещё точно не знаем, где оно начинается и где заканчивается).

| Способность исполнять код i8086 (IA16) | 1 |

| Частичная паралеллизация исполнения команд, специализация ФУ | 2 |

| Поддержка виртуальной памяти, многозадачности и 32-битности (IA32) | 2 |

| L1-кэш | 2 |

| Исполнительный конвейер | 2 |

| Встроенный FPU | 3 |

| Умножитель частоты ядра | 3 |

| IPC=2, специализация L1 | 1,6 |

| Конвейризованный FPU | 3 |

| SIMD: 4/2/1-байтовые целые | 2 |

| OoO и/или НТ | 1,3 |

| SIMD: вещественные одинарной точности | 1,4 |

| Встроенный L2-кэш | 1,4 |

| IPC=3 | 1,25 |

| SIMD: вещественные двойной точности, 8/4/2/1-байтовые целые | 1,4 |

| Многоядерность | 1,5 |

| Встроенный контроллер памяти | 1,2 |

| Встроенный L3-кэш | 1,2 |

| 64-битность (x86-64) | 1,2 |

| IPC=4 | 1,15 |

| Технология TurboBoost | 1,1 |

А теперь детальнее о том, почему цифры именно такие:

- Способность исполнять код i8086 (IA16). Как такового коэффициента тут нет, просто производительность 8086 взята за единицу, которая далее будет умножаться на бо́льшие коэффициенты.

- Частичная параллелизация исполнения команд, специализация ФУ, а также…

- Поддержка виртуальной памяти, многозадачности и 32-битности (IA32). Эти два пункта взяты от i286/386 (дань попытке №1). Чем эти процессоры отличаются от i8086, детально описано по ссылке выше, а как это влияет на скорость, показывали реальные замеры и среднее число тактов для выполнения команды — в обоих случаях примерно вдвое быстрее. Отдельно упомянем удвоение разрядности — при вычислении 32-битных чисел пользы у 32-битности даже больше, чем на одно только удвоение скорости, но не все программы 100% времени занимаются лишь одними 32-битными вычислениями.

- L1-кэш. Тут уже посложнее. Впервые кэш L1 у x86 CPU появился во времена 386-х — именно тогда обнаружилось более выраженное ускорение частот логических схем (т. е. ЦП) по сравнению со схемами памяти. Потому приходилось вставлять дополнительные такты ожидания при обращении в память, которая на частотах 25 МГц и выше уже не успевала возвращать данные за 2 такта (таков макс. темп шины данных у 286 и 386). Даже удвоение очереди предзагрузки команд в 386 до 12 байт не сильно помогло: вдвое быстрый процессор вдвое чаще ожидает поступления очередной команды — а ведь шина «ЦП-память» нужна ещё и для данных. С учётом дальнейшего повышения частот за счёт умножения частоты ЦП вклад кэша (на тот момент срабатывавшего за 1 такт) в общую производительность решено считать 2-кратным.

- Исполнительный конвейер. Появившись впервые в 486 (считая однокристальные CISC-ЦП), конвейер позволил довести производительность за такт до максимально возможного значения для несуперскалярного процессора — 1 такт/команду (в среднем 1,5), что оказалось вдвое быстрее предыдущих ЦП. Это косвенно подтверждает распространённый тогда бенчмарк iCOMP, показавший 100 баллов на i80486SX 25 МГц (именно к этому ЦП и привязали величину «попугая» iCOMP) и 49 — на i80386DX 25 МГц. (Кстати, вы уже заметили, что в таблице для процессоров до 486 параметр «Конвейеры (IPC)» указан как 0 — это значит не то, что процессор делает ноль команд за такт, а то, что IPC всегда меньше 1, хоть и больше 0, потому что число исполнительных конвейеров — именно ноль. Ну а «4+1» для процессоров Intel Core 2 и Core i7 означает, что в крайне редких случаях, которые мы не учитываем, эти ЦП способны обрабатывать 5 команд/такт.)

- Встроенный FPU. На 4-8-кратное ускорение при переходе от внешнего FPU к внутреннему указывают такты исполнения команд в i80387 (последний внешний сопроцессор, не считая «нечестного» 487 и крайне редкого Nexgen Nx587) по сравнению с i80486DX, где FPU уже внутри. Однако тот же iCOMP показывает всего 122 балла для i80486DX по сравнению с 100 баллами для i80486SX на одних и тех же 25 МГц. Поскольку вещественные вычисления также занимают не все 100% времени даже в тех программах, где они есть, мы грубо уполовинили это значение, приняв коэффициент 3.

- Умножитель частоты ядра. Число 3 указано как максимальный коэффициент, достигнутый большинством производителей ЦП в том их поколении, когда они внедрили эту штуку. Нелинейное ускорение за счёт повышения нагрузки на шину «ЦП-память» (а ПСП растёт далеко не так резво) компенсировалась увеличением кэшей, внедрением отложенной записи вместо сквозной и некоторыми другими «костылями».

- IPC=2, специализация L1. Вот здесь начинается самое интересное. Т. к. способа отключить «лишний» конвейер нет, приходится сравнивать наиболее близкие ЦП по скорости. Итак, i80486DX4 100 МГц набирает 51 балл в SPECint92, 27 в SPECfp92 и 435 по тесту iCOMP. А вот 66 МГц Pentium: 64.5 в SPECint92, 56.9 в SPECfp92 и 567 в iCOMP. Объём L1 у этих ЦП одинаковый (но у 486 L1 общий, а у P5 — раздельный, с параллельным доступом к L1D и L1I), отложенная запись есть у обоих, а конвейеризованный FPU оставим на потом. Что ещё есть у Pentium? Учетверённая ПС шины (вдвое по частоте и по разрядности), предсказатель ветвлений и почти тот же 5-стадийный целочисленный конвейер, что и у i486 — но в двух экземплярах. Глядя на целочисленное ускорение на 90-95 % (после поправки на частоту), следует сделать вывод, что хорошо оптимизированные программы могут получить почти линейный рост скорости при добавлении второго конвейера (что не обязательно для последующих). Реальное среднее ускорение не полностью или не всегда оптимизированного кода аккуратно предлагаем считать как 60% от максимально достигнутого, отсюда коэффициент 1,6.

- Конвейеризованный FPU. Коэффициент 3 получается как исходя из указанных выше цифр по SPECfp92, так и по тактам работы FPU i80486DX и Pentium. Причём, в отличие от предыдущего случая, на 1/3 мы не сокращали, т. к. на тот момент вещественные вычисления были всё ещё уделом профессиональных программ, написанных профессиональными программистами — со всеми нужными оптимизациями.

- SIMD: 4/2/1-байтовые целые (в таблице — «4i»). Множитель 2 тут получился по причине среднего ожидаемого ускорения от векторных вычислений с MMX-оптимизацией. При использовании 32-битных целых в каждом векторе их умещается по два, но при этом далеко не каждая операция действительно является векторной (скалярные действия занимают существенную часть даже плотного векторного кода), более того — не каждая операция является именно вычислительной и именно с данными. С другой стороны, при использовании 16- и 8-битных целых скорость более чем удваивается. Предполагая примерно равную долю этих случаев, возьмём цифру 2.

- OoO и/или НТ. Мало того, что отключить OoO мы не можем, так ещё и нет более-менее похожих по архитектуре ЦП с и без OoO, для которых можно было бы однозначно оценить скорость. Однако это можно сделать для гиперпоточности. Глядя на процессор Atom, в который Intel решила ввести не OoO, а именно НТ, становится очевидна главная роль обеих технологий — подтяжка скорости ЦП до той, которая была бы при оптимальной оптимизации кода. Таким образом тут нам надо добавить ранее отрезанную треть, откуда и получился коэффициент 1,3, хорошо согласующийся с тестами Atom с и без НТ. Однако внимательный читатель (у нас ещё такие остались?…) сразу перемножит 1,6 от «IPC=2» и 1,3 от «OoO и/или НТ», получив 2,08. Это что же, ЦП с двумя конвейерами и их «ускорялкой» может получить более чем двукратное ускорение по сравнению с одноконвейерными коллегами? Да, потому что и OoO, и НТ применимы даже к одному конвейеру (хотя ускорять его почти некуда).

- SIMD: вещественные одинарной («SP») точности. Тут ситуация усложняется тем, что таких технологий было две — малопопулярная первопроходчица 3DNow! с шириной вектора в два элемента и чуть более поздняя и вдвое более широкая SSE. (О попытках Cyrix и прочих товарищей добавить свои аналогичные команды упоминать не будем — опросив прохожих, проштудировав полное собрание сочинений Винера и прослушав все обращения президента к Федеральному собранию авторы не обнаружили даже названий этих наборов. [Лодыри, EMMX он назывался, там было 12 команд, как сейчас помню… — Прим.ред.]) Но коэффициенты 2 и тем более 4 будут преувеличенными — число скалярных и невычислительных операций на тот момент было ещё велико (особенно без команд перетасовки, появившихся позже), да и одинарная точность не всегда достаточна. Ну а 128-битные ФУ появились лишь спустя годы после внедрения 128-битных векторов, так что первый SSE выигрывал у 3DNow! в основном за счёт того, что его отдельные регистры не отнимают хлеб у MMX и стека FPU. Итоговое ускорение приняли за 1,4.

- Внутренний L2-кэш. При наличии кэша любого уровня на плате встраивание его в ЦП (с некоторыми оговорками о том, к чему это иногда приводит) преследует две цели — резкое увеличение ПС кэша и возможность одновременных операций на шинах «ядро-память» и «ядро-кэш». В эпоху первых модулей SDRAM PC-66 и PC-100 переселение L2 поближе к ядру улучшало латентность и ПСП в 2-4 раза, что, с учётом частоты промахов L1 в 5-10 % и темпе обращений в 1-1,5 слова/такт, давало по началу около 30% ускорения. Но эта величина увеличивалась с ростом частоты ЦП, за которой ускорялся и набортный L2 (быстрее, чем если бы он остался на плате). Так что итоговый коэффициент получился 1,4.

- IPC=3. Ускорение от очередного конвейера решено приблизительно считать квадратным корнем от максимально возможного (в данном случае — +50% по сравнению с IPC=2) по причине трудностей в подборе более двух команд для одновременного исполнения и возможного отсутствия либо исполнительных ресурсов, либо данных для них. Отсюда множитель 1,25.

- SIMD: вещественные двойной («DP») точности, 8/4/2/1-байтовые целые («8i»). Смысл множителя 1,4 тут примерно тот же, что и с SIMD одинарной точности — удвоение скорости на SP достигается за счёт поголовного (к этому моменту) внедрения 128-битных векторов, куда умещается 4 SP-элемента, а вот ускорение двойной точности куда меньшее и примерно равно тем же 40%. Итоговый коэффициент такой же, как и с SP, т. к. скалярных вычислений и с SP, и с DP, а также подготовительных неарифметических операций никто не отменял.

- Многоядерность. Тут всё просто: по нашим недавним тестам 2-ядерность (а многоядерность долгое время была именно такая) на данный момент приносит в среднем +50% к «одноядерной» скорости. На момент её внедрения она приносила ещё меньше, но, с другой стороны, двумя ядрами мы теперь не ограничиваемся.

- Встроенный контроллер памяти, а также…

- Встроенный L3-кэш. Такие же взаимодополняемые, как и пара «OoO и/или HT», обе эти «примочки» нужны для компенсации большой латентности и (в меньшей степени) низкой ПСП, когда ресурсов L1 и L2 уже не хватает. По результатам тестов решено оба множителя приравнять к 1,2.

- 64-битность (x86-64). Одно только удвоение числа регистров даже без всяких 64-битных вычислений способно почти двукратно ускорить некоторые задачи. Но т. к. такая оказия возникает редко, да и оптимизация идёт весьма медленно, итоговый разгон очень разнится: он был равен в среднем 10-15 % в 2006 г. и, предположительно, около 20% сегодня.

- IPC=4. Очевидные из вышесказанного 15% введены по настоятельной просьбе одной компании, имя который она попросила не называть. ;)

- Технология TurboBoost. Единственный пункт, добавленный к предыдущим из ранних попыток. +10% получены в результате наших собственных замеров, хотя вышеупомянутая компания осталась ими недовольна и решила больше к нам не заходить. :)

После перемножения множителей всех имеющихся для каждого ЦП «улучшайзеров» мы получаем число 86-х, которые данный процессор «съедает» каждый такт. Поскольку мы не складываем коэффициенты, а перемножаем, производительность растёт в геометрической прогрессии, а потому оценивать мы её будем по логарифмической шкале. И так как измеряем мы не рейтинг «Единой России», а скорость вычислительной машины, основание логарифма будет самое правильное — 2. Правда, номер поколения тогда растёт неожиданно быстро, а потому волевым решением мы его уполовиним. Итого, финальная формула получилась следующей:

| G=[log2(P)]⁄2+1 |

Тут P — рассчитанная выше скорость (произведение коэффициентов), квадратные скобки — округление до целых, а 1 добавляется по причине привычного счёта поколений с единицы (всё-таки…). Немного перетасовав процессоры по группам и заменив каждые «пять десятых» на «+», мы получаем … (барабанная дробь!) … получаем мы …

Классификация третья, «скоростная»

| ЦП | Поколение G [скорость P] | FPU: Внешний, (Не)Конвейерный | Множитель | SIMD | Конвейеры (IPC) 3 | OoO, HT | Многоядерность | Макс. уровень кэша в ЦП | Контроллер памяти | Виртуальная память, многозадачность | Разрядность адресации 1 |

| …86/88 (все) | 1 [1] | В | − | − | 0 | − | − | 0 | − | − | 20 |

| …286 (все) | 1+ [2] | В | − | − | 0 | − | − | 0 | − | − 2 | 24 |

| …386… (кроме указанных ниже) | 2 [4] | В | − | − | 0 | − | − | 0 | − | + | 32 |

| IBM 386SLC; Chips&Technologies 38605DX | 2+ [8] | В | − | − | 0 | − | − | 1 | − | + | 32 |

| Intel RapidCAD | 3+ [24] | НК | − | − | 1 | − | − | 0 | − | + | 32 |

| Intel i80486SX; AMD Am486SX; IBM 486BLX/DLC/SLC; Cyrix Cx486SR…/D…/S…; Texas Instruments TI486SX…; UMC U5S… | 3 [16] | В | − | − | 1 | − | − | 1 | − | + | 32 |

| …486DX…/SLC/BLX (остальные, без цифры); UMC U5D… | 4 [48] | НК | − | − | 1 | − | − | 1 | − | + | 32 |

| …486DLC…/SLC…/BLX… /S…/SX(L)…/DR… /SR… (с цифрой) | 4 [48] | В | + | − | 1 | − | − | 1 | − | + | 32 |

| …486(BL)DX… (с цифрой); …5x86… | 4+ [144] | НК | + | − | 1 | − | − | 1 | − | + | 32 |

| Intel Pentium | 5+ [691] | К | + | − | 2 | − | − | 1 | − | + | 32 |

| Intel Pentium MMX | 6 [1382] | К | + | 4i | 2 | − | − | 1 | − | + | 32 |

| Intel Pentium Pro | 6+ [1572] | К | + | − | 3 | OoO | − | 2 | − | + | 36 |

| Intel Pentium II | 7 [3145] | К | + | 4i | 3 | OoO | − | 2 | − | + | 36 |

| Intel Pentium III | 7 [4403] | К | + | SP+4i | 3 | OoO | − | 2 | − | + | 36 |

| Intel Pentium 4/M | 7+ [6164] | К | + | DP+8i | 3 | OoO | − | 2 | − | + | 36 |

| Intel Atom | 7+ [8876] | К | + | DP+8i | 2 | НТ | + | 2 | − | + | 64 |

| Intel Core | 7+ [9246] | К | + | DP+8i | 3 | OoO | + | 2 | − | + | 36 |

| Intel Pentium D/EE | 7+ [11095] | К | + | DP+8i | 3 | обе | + | 2 | − | + | 64 |

| Intel Core 2 | 8 [12760] | К | + | DP+8i | 4~5 | OoO | + | 2 | − | + | 64 |

| Intel Core i7 | 8 [20211] | К | + | DP+8i | 4~5 | обе | + | 3 | + | + | 64 |

| IDT WinChip C6(+) | 5 [288] | НК | + | 4i | 1 | − | − | 1 | − | + | 32 |

| IDT WinChip 2 | 6 [1210] | К | + | SP+4i | 1~2 | − | − | 1 | − | + | 32 |

| AMD K5, 5k86 | 6 [899] | К | + | − | 2~4 | OoO | − | 1 | − | + | 32 |

| AMD K6 | 5+ [599] | НК | + | 4i | 2 | OoO | − | 1 | − | + | 36 |

| AMD K6-2 | 6 [839] | НК | + | SP+4i | 2 | OoO | − | 1 | − | + | 36 |

| K6-2+, K6-III | 6 [1174] | НК | + | SP+4i | 2 | OoO | − | 2 | − | + | 36 |

| AMD Athlon (K7), XP | 7 [4403] | К | + | SP+4i | 3 | OoO | − | 2 | − | + | 36 |

| AMD Athlon 64 (K8) | 8 [13315] | К | + | DP+8i | 3 | OoO | + | 2 | + | + | 64 |

| AMD Phenom (K10) | 8 [15977] | К | + | DP+8i | 3 | OoO | + | 3 | + | + | 64 |

| Cyrix 6x86/M1(R) | 5 [300] | НК | + | − | 2 | OoO | − | 1 4 | − | + | 32 |

| Cyrix 6x86MX (M II) | 5+ [599] | НК | + | 4i | 2 | OoO | − | 1 4 | − | + | 32 |

| VIA C3 | 6+ [1693] | К | + | SP+4i | 1 | − | − | 2 | − | + | 32 |

| VIA C7 | 6+ [2371] | К | + | DP+8i | 1 | − | − | 2 | − | + | 32 |

| VIA Nano | 7+ [7397] | К | + | DP+8i | 3 | OoO | − | 2 | − | + | 64 |

| Rise mP6 | 6 [1382] | К | + | 4i | 2~3 | − | − | 1 | − | + | 32 |

| Transmeta Crusoe | 7 [3019] | К | + | 4i | 2~4 | 5 | − | 2 | + | + | 32 |

| Transmeta Efficeon | 7+ [7397] | К | + | DP+8i | 3~8 | 5 | − | 2 | + | + | 32 |

| NexGen Nx586 | 3+ [29] | В | − | − | 1 | OoO | − | 2 6 | − | + | 32 |

| NexGen Nx686 | 6 [839] | НК | + | 4i | 2 | OoO | − | 2 6 | − | + | 32 |

1 — реальная или виртуальная (при наличии виртуальной памяти) ↑

2 — неудачная реализация, практически не использовалась ↑

3 — указано используемое в подсчёте число IPC. Если оно отличается от фактического, но редко применимого, то последнее указано после тильды. Например, для WinChip 2 IPC=2 только для наиболее простых и частых команд MMX, а у других процессоров «с тильдой» официальное число IPC достижимо лишь на смешанных цело-вещественных операциях ↑

4 — общий кэш L1 ↑

5 — исполняется «сверхдлинное машинное слово» (VLIW), преобразованное из кода x86 с перетасовкой команд при формировании. Их число в слове указано в столбце IPC после тильды. До тильды — ожидаемое значение IPC ↑

6 — L2 внешний, но подключён через отдельную шину, которая может работать на частоте ядра ↑

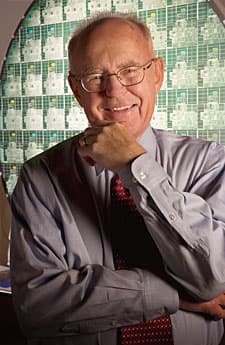

Ему бы она, наверное, понравилась…

Этого господина (если кто не в курсе) зовут Гордон Мур, и известен он публике прежде всего по эмпирической закономерности имени себя (именуемой в народе «законом») об удвоении числа транзисторов в микросхеме каждые 2 года. Правда, за более чем полвека существования этого закона его успели переврать как по цифре (иногда говоря об удвоении за 1,5 года), так и по характеристике (говоря о скорости процессора, а не о числе транзисторов). И поскольку потребитель покупает не транзисторы и даже не мегагерцы, а именно производительность, предположим, что каждые 2 года удваивается именно она. А теперь проверим, что нам напредсказывал мистер Мур, и как оно соблюдалось за 30 лет существования архитектуры x86 — согласно нашей свежеиспечённой классификации по скорости:

| ЦП | Год 1 | Скорость (рейтинг) | Скорость по Муру |

| …86/88 (все) | 1978 | 1 | 1 |

| 1979 | |||

| 1980 | 2 | ||

| 1981 | |||

| …286 (все) | 1982 | 2 | 4 |

| 1983 | |||

| 1984 | 8 | ||

| …386… (кроме указанных ниже) | 1985 | 4 | |

| 1986 | 16 | ||

| 1987 | |||

| 1988 | 32 | ||

| …486DX… (без цифры); UMC U5D… | 1989 | 48 | |

| 1990 | 64 | ||

| IBM 386SLC, 486DLC/SLC; Chips & Technologies 38605DX | 1991 | 8 | |

| Intel i80486SX; AMD Am486SX; IBM 486BLX; Cyrix Cx486SR…, Cx486D/S…; Texas Instruments TI486SX…; UMC U5S… | 16 | ||

| IBM 486DLC2/SLC2 | 1992 | 24 | 128 |

| Intel RapidCAD | 24 | ||

| …486DX…/BLX…/DLC… (с цифрой); AMD Am5x86 X5 | 144 | ||

| Intel Pentium | 1993 | 691 | |

| NexGen Nx586 | 1994 | 47 | 256 |

| Intel Pentium Pro | 1995 | 1572 | |

| Cyrix 5x86/M1sc; IBM 5x86C | 144 | ||

| NexGen Nx686 | 839 | ||

| AMD K5, 5k86 | 1996 | 899 | 512 |

| Cyrix 6x86/M1(R) | 300 | ||

| Intel Pentium MMX | 1997 | 1382 | |

| Intel Pentium II | 3145 | ||

| AMD K6 | 599 | ||

| Cyrix 6x86MX (M II) | 599 | ||

| IDT WinChip C6(+) | 1998 | 288 | 1024 |

| AMD K6-2 | 839 | ||

| Rise mP6 | 1382 | ||

| Intel Pentium III | 1999 | 4403 | |

| IDT WinChip 2 | 1210 | ||

| K6-2+, K6-III | 1174 | ||

| AMD Athlon (K7), XP | 4403 | ||

| Intel Pentium 4/M | 2000 | 6164 | 2048 |

| VIA C3 | 1693 | ||

| Transmeta Crusoe | 3019 | ||

| 2001 | |||

| 2002 | 4096 | ||

| AMD Athlon 64 (K8) | 2003 | 13315 | |

| Transmeta Efficeon | 7397 | ||

| Intel Pentium D/EE | 2004 | 11095 | 8192 |

| VIA C7 | 2005 | 2371 | |

| Intel Core | 2006 | 9246 | 16384 |

| Intel Core 2 | 12760 | ||

| AMD Phenom (K10) | 2007 | 15977 | |

| Intel Atom | 2008 | 8876 | 32768 |

| Intel Core i7 | 20211 | ||

| VIA Nano | 7397 |

1 — для групп ЦП дан год появления самого раннего ↑

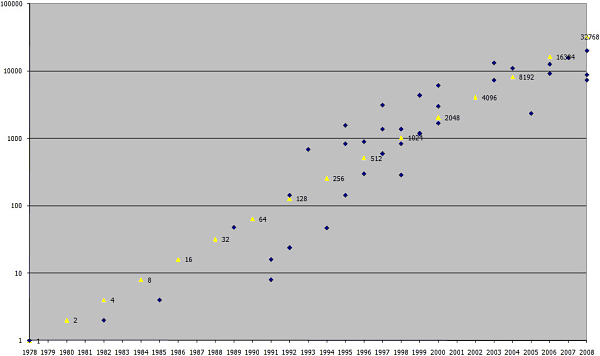

Проще представить эту информацию в виде графика. Тут жёлтые маркеры олицетворяют собой «закон» Мура, синие — реальные процессоры и их скорость P согласно последнему варианту классификации.

Итак, если наши подсчёты верны, то в 80-е годы всё шло ожидаемо, в 90-е ударники капиталистического труда перевыполняли план в разы, а в уходящих 2000-х картина грустная. Поможет нам набор команд AVX с удвоенной шириной векторов, который позволит ускорить производительность ещё процентов на сорок — как раз до «8+»-поколения. Но к 2011 г., когда это, предположительно, произойдёт, неутомимый мистер Мур будет требовать от производителей ЦП (и прежде всего — от Intel, где он всё это время работает, и сооснователем которой является) уже сотню тысяч 86-х, а это уже «9+»…

Помимо прочего, глядя на таблицу, напрашиваются любопытные выводы:

- Самым крупным прыжком среди процессоров Intel был 486-й. Увеличив скорость аж в 12 раз (так мы посчитали…), он преодолел 2 поколения, т. е. 4 полушага. Также был силён Pentium — после 486DX… это даже не «5», а «5+». Остальные поколения компания проходила подряд, по всем остановкам на каждом полушаге.

- Технологии MMX оказалось достаточно, чтобы затащить вышеупомянутый ЦП в 6-е поколение, хоть и без плюса. По крайней мере все его главные конкуренты по производительности относили себя именно «туда».

- Pentium III надо было называть как угодно, но не Pentium III. Скажем, Pentium II+. Ибо недостоин.

- Все виды Pentium 4 волшебным образом попали под одну гребёнку под номером 7+. Т. е. как не старайся, но ничего большего из микроархитектуры Netburst вытянуть не удалось.

- В названиях ЦП других компаний часто встречаются цифры, которые (не считая самонадеянной Cyrix) чаще всего вполне соответствуют поколению по этой методике.

- AMD явно промахнулась, отказавшись от конвейерного FPU при переходе от K5 к K6. Купив NexGen с её полуготовым Nx686, AMD изготовила «процессор шестого поколения», который поначалу оказался хуже и самого Nx686, и собственного K5 (а он-то как раз полноценный «шестой»).

- А вот K7 и K8 получились замечательно. По сравнению с ними Phenom в лучшем случае K8¼, но никак не K10.

- После покупки Cyrix фирма VIA решила отказаться в угоду векторности и энергоэффективности не только от OoO, но даже и от суперскалярности — и, как ни странно, до поры до времени это вполне неплохо работало (сравните с 3-конвейерным Pentium Pro).

- Transmeta Efficeon явно опередил своё время. Сделать бы его многоядерным (хотя бы и двумя чипами в корпусе) и 64-битным, да ещё и по 65-45 нм — и было бы куда труднее жить не только Intel Atom (а Transmeta создавала ЦП прежде всего для мобильных применений), но и более мощным Core 2 и K8.

- NexGen — пожалуй, самая романтичная компания на этом рынке. Она создала всего два процессора, и оба оказались одновременно техническим прорывом, ненадолго заткнувшим за пояс даже саму Intel, и коммерческим провалом из-за крайней неприспособленности к реальным требованиям рынка. Даже выскочка Rise с вполне приличным (для новичка) mP6 оказалась коммерчески более удачной, а Nx686 вообще не дошёл до массового производства. Но мы всё равно решили включить эти раритеты в классификацию для полноты.

Разумеется, всё может быть совершенно иначе, и мы опять, в третий раз что-то напутали… Однако, дабы не повторять ошибок, заранее подготовимся и напишем ответы на:

Вопросы, которые, как мы думаем, будут часто задаваемы

Q: А почему вы учитываете лишь производительность за такт, но не частоту?

A: Как вы наверняка помните из статьи о производительности, частота прежде всего зависит от техпроцесса, а уж потом от архитектурных ограничений. Конечно, внедрение конвейеров и увеличение числа их стадий здорово помогает, но итоговая достигнутая частота больше скажет о не самом ЦП, а о достижениях микроэлектронного завода, где он выпускался. Тем не менее, технологию TurboBoost нам всё же пролоббировали…

Q: А почему у вас процессоры X и Y набирают одинаковое число баллов или вовсе записаны в одной клетке, когда внутри они совершенно разные?

A: Потому что мы замеряем итоговую скорость (иногда — пытаемся угадать) вне зависимости от того, какими способами она достигнута.

Q: Почему я не вижу в списке технологию T? Ведь она так круто ускоряет процессор Z!

A: Наверное, подзабыли. Расскажите нам о ней в цифрах (раз уж речь идёт об ускорении).

Q: А по-моему, технология T даёт коэффициент совсем не K, как у вас!

A: Возможно. Приведите свои цифры и их обоснование, тогда будет что обсуждать.

Q: Да кому вообще нужна эта ваша классификация?! Процессоры работают и без неё!

A: Видите ли, мы и сами вовсе не настаиваем на том, что она нужна. Хотя вполне допускаем такую возможность. Если она не нужна конкретно вам — мы совершенно не возражаем. Для нас же оказалось важно, что теперь каждый новый ЦП можно рассматривать именно с такой точки зрения — что бы там не добавили, если это не даёт хоть чуток скорости, то это в лучшем случае второстепенная изюминка; а вот если даёт — то не так уж и важно, какой там сорт изюма ;)

Q: А чего это в вашей классификации нет моего нового процессора? Он порвёт всех, я точно знаю!

A: Здравствуйте, Борис Арташесович! Мы тоже очень рады, что Вы нас читаете! :)

Q: Да у вас всё неверно! RTFM!

A: Спасибо, и вам тоже приятного чтения. Будем счастливы увидеть более конкретные замечания.