На прошедшей в Вашингтоне конференции IEDM (IEEE International Electron Devices Meeting), AMD рассказала о своем видении будущего полупроводниковых технологий. На наш взгляд, наиболее любопытным является анализ перспектив применения технологий SOI (silicon-on-insulator, кремний-на-изоляторе) и диэлектриков с низкой диэлектрической проницаемостью (low-k) для выпуска полупроводниковых чипов по 45-нм нормам.

На сегодняшний день длина затвора полевого транзистора в процессорах AMD достигает 50 нм, в то время как для 45-нм по требованиям ITRS необходимо достичь размеров 20 нм. Для достижения этих требований, AMD, во-первых, планирует использовать трехзатворный подход. Ранее о своих разработках трехмерных транзисторов уже сообщили IBM и Intel.

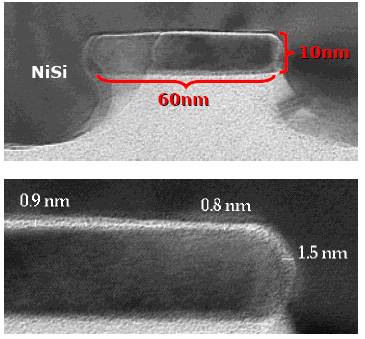

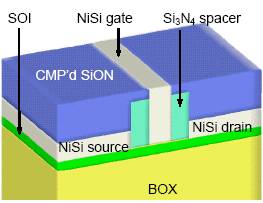

Во-вторых, планируется использование технологии полностью истощенного полупроводника на диэлектрике (FDSOI), позволяющего еще больше снизить ток утечки по сравнению с SOI. В-третьих, затвор транзисторов планируется изготавливать из хорошо проводящего силицида никеля (NiSi) вместо поликристаллического кремния, и в-четвертых, проводящий канал будет выполнен по технологии локального напряжения (locally strained channel) для улучшения подвижности электронов.

Отличительной особенностью SOI-технологий AMD является малая диэлектрическая проницаемость изолирующих пленок, в то время как многие производители работают с пленками с высокой диэлектрической проницаемостью.