MIPS Technologies объявила о выпуске нового "лицензируемого" 64-битного ядра MIPS64 20Kc, предназначенного для работы в экономичных и недорогих игровых и телевизионных приставках, мультимедийных приложениях, а также в устройствах автомобильной телематики.

Новое 64-битное процессорное ядро с тактовой частотой до 600 МГц будет производиться с использованием 0,13 мкм техпроцесса и обладает производительностью до 1370 Dhrystone, 2,1 GFLOPS (млрд. операций с плавающей точкой в секунду). По заявлению MIPS, архитектура ядра 20Kc может быть масштабирована на производство с нормами 0,10 мкм техпроцесса с увеличением тактовой частоты до 1 ГГц. В настоящее время выпускаются 400 МГц версии чипа на мощностях партнера компании, тайваньской TSMC, с применением 0,18 мкм норм.

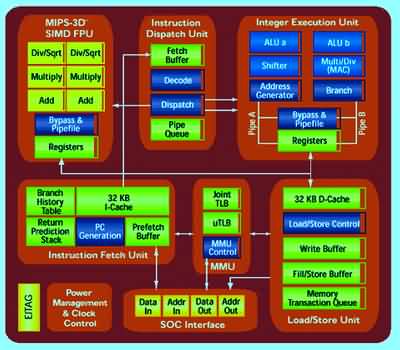

Ядро 20Kc обладает двумя 7-стадийными конвейерами, блоками вычислений с целыми и числами с плавающей запятой, поддерживает SIMD инструкции. Процессор оборудован двумя 32 Кб кэшами, новой масштабируемой SoC шиной MGB Link с максимальной пропускной способностью до 3,6 Гб/с. 600 МГц процессор при напряжении питания 1 В будет рассеивать всего 1,5 Вт.