Компания Intel объявила о готовности к выпуску в начале 2011 года процессоров новой архитектуры Sandy Bridge («песчаный мост»), которая придёт на смену текущим Nehalem (45 нм) и Westmere (32 нм). В соответствии с правилом выпуска «тик-так», Sandy Bridge является «та́ком» — новой микроархитектурой, выпущенной на уже отработанном техпроцессе (32 нм). Впрочем, уже в конце 2011 года ожидается очередной «тик» — чуть обновлённая 22-нанометровая версия Sandy Bridge под названием Ivy Bridge (плющевый мост). Ну а сейчас, разбираясь с песчаным детищем, в качестве эксперимента попробуем новый подход — используем оригинальные иллюстрации из презентаций Intel (разумеется, не все и не целиком), но прокомментируем их по-нашему :)

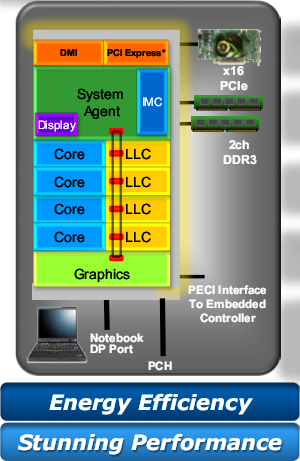

Итак, нам предлагают процессоры, построенные (держитесь крепче!) вокруг «энергоэффективности» и «сногсшибательной производительности» — самый лучший способ заставить читателя заснуть от скуки на этом самом месте. Впрочем, вот краткий список реальных достоинств по сравнению с текущим поколением ЦП Intel:

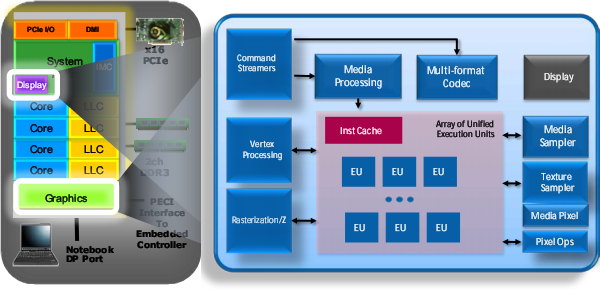

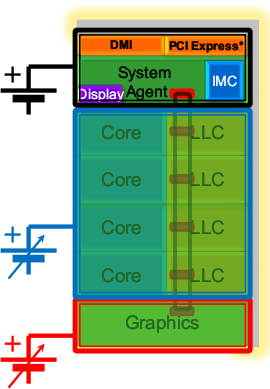

- В чип теперь встроен северный мост чипсета вместе с видеоядром.

- Само графическое ядро (GPU) обновлено, но при этом оставлена возможность подключить и внешнюю графику.

- Ядра общего назначения поддерживают расширение AVX.

- Кэш L3 увеличил пропускную способность за счёт высокоскоростного подключения к ядрам (в т. ч. к GPU).

- Технология авторазгона TurboBoost улучшена.

Вот по этим и более мелким пунктам и пройдёмся.

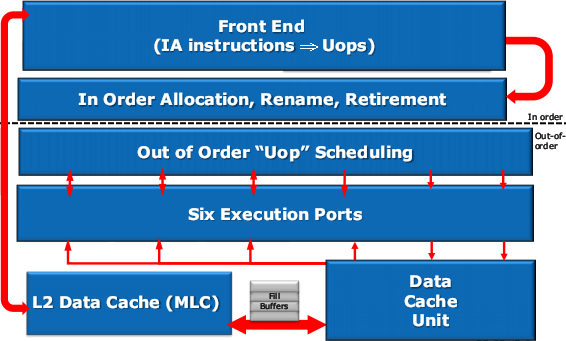

Крупноблочно ядро ЦП не изменилось. Всё дело в деталях.

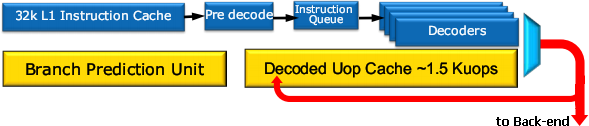

Во фронте главное нововведение — кэш на 1536 мопов, буферизирующий результаты работы декодеров. Также переработан предсказатель переходов, хранящий теперь вдвое больше целевых адресов и более долгую историю поведения команд. К нему подключен блок, определяющий попадания в моп-кэш, и в этих случаях кэш L1I, предекодер-длиномер и декодеры отключаются, экономя энергию. Также увеличивается производительность за счёт улучшения реакции на неверно предсказанный переход (правильная ветвь может оказаться в моп-кэше) и освобождения от необходимости декодировать длинные команды за несколько тактов при каждом их исполнении.

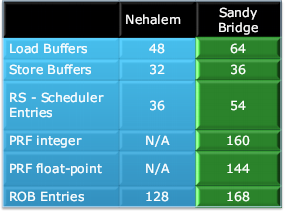

Тыл конвейера поменялся сильнее. Первое явное изменение: переход от полного буфера ROB (хранящего мопы и значения меняемых ими регистров) к комбинации сокращённого ROB (хранящего только мопы в оригинальном порядке) и двух физических регистровых файлов (PRF, хранящих содержимое переименованных регистров, на которые мопы ссылаются) — целочисленного и векторно-вещественного. Смысл перехода в том, что вместо пересылок мопов вместе с данными пересылаются только ссылки на регистры, а сами мопы и данные остаются на месте вплоть до отставки — в результате удаления ненужных пересылок экономится энергия. А за производительность отвечает вполне дежурное увеличение размеров всего разнообразия буферов и очередей.

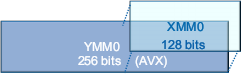

На уровне функциональных устройств главная новость — поддержка AVX, нового дополнения системы команд x86-64. В отличие от очередного SSE, просто добавляющего новые команды, AVX позволяет:

- обращаться к 256-битным векторным регистрам ymm, расширяющим привычные xmm для SSE;

- использовать во всех векторных командах 3-4 операнда в недеструктивной форме, когда результат операции не уничтожает исходные аргументы;

- сэкономить на размере векторных команд за счёт компактизации кода (особенно для SSSE3 и далее).

Разумеется, есть и новые инструкции — для распределения элементов в векторе и маскированных операций с памятью.

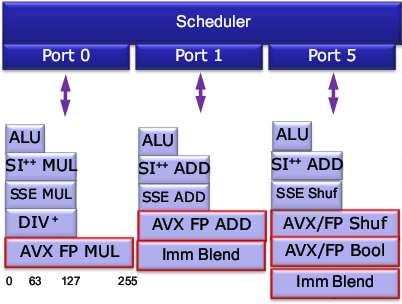

Чтобы благие начинания не остались только на уровне распознавания команд AVX, блок ФУ переделан для обработки регистров ymm с такой же скоростью, как и xmm. Для этого 128-битные сумматор, умножитель, АЛУ и перетасовщики удвоили разрядность, соответственно подняв пиковую производительность ядра.

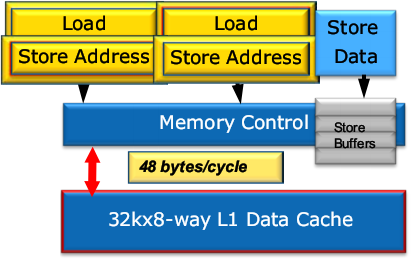

Кэш L1D на 50% повысил полную пропускную способность — теперь это 32 байта чтения + 16 байт записи за такт. Для этого в LSU (контроллер L1D) поставлен второй 16-байтовый порт чтения. Это позволит в нужном темпе насыщать ФУ данными при исполнении AVX-кода.

Из прочих обновлений ядра, не удостоившихся места на диаграммах, — ускорение нескольких команд, важных для задач шифрования, а также сохранения состояния процессора при переключении контекста задачи в ОС.

Во внеядре (так Intel называет остальную часть ЦП, не вошедшую в ядра общего назначения) список изменений открывает как-бы-новая (появившаяся ещё в марте 2010 г. в 8-ядерных серверных чипах Nehalem-EX) 32-байтовая кольцевая шина, связывающая кэш L3, вычислительные и графическое ядра и «системный агент» (бывший северный мост с ИКП для памяти типа DDR3). L3, обозначенный как LLC (last level cache, кэш последнего уровня), состоит из нескольких банков (по числу ядер общего назначения) с портом доступа в каждом. Связывающая всё это кольцевая шина работает на частоте, сравнимой с частотой ядер, и в идеале за такт передаёт количество данных, равное произведению 32 на число банков. Этим способом производительность разделяемого L3 увеличивается пропорционально числу ядер, а вот обещанное уменьшение задержек (по крайней мере в тактах) сомнительно по сравнению с централизованным контроллером L3.

Поскольку GPU теперь располагается на чипе процессора, а не на отдельном, как в нынешних Core i3/i5, кэш L3 может быть использован в т. ч. и для графики, что сглаживает недостаток пропускной способности системной памяти по сравнению со специализированной видеопамятью, редко доступной для встроенного GPU.

Видеоядру обещана удвоенная производительность, и не только за счёт быстрого кэша L3, но и от удвоения числа исполнительных блоков до 12 — правда, не во всех моделях, о чём на диаграммах умалчивают. Также внедрена поддержка DirectX 10 (а на дворе уже 11-й…) и новых форматов HD-видео для энергоэффективного аппаратного ускорения

ЦП будет получать тройное питание — для ядер общего назначения и L3, для GPU, а также для системного агента с контроллерами всевозможных шин. Пока не ясно, имеют ли все линии автоподстройку под текущую загрузку, т. к. на приведённом слайде напряжение системного агента указано как фиксированое, а в тексте к другому написано, что регулировать можно все вольтажи.

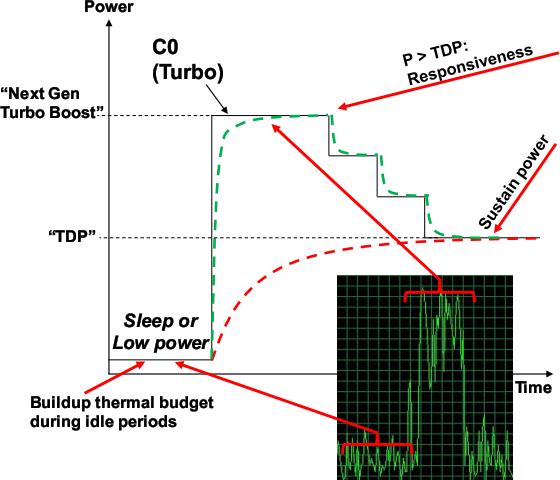

Контроллер терморежима и питания реализует обновлённую версию технологии TurboBoost, учитывающую переходные процессы. Она позволит в течение короткого времени (20–60 с) разогнать ядра (включая GPU) до частот, при которых тепловыделение даже выше номинального пика (TDP), если до этого ЦП некоторое время простаивал. Это обеспечит бо́льшую отзывчивость коротким по времени выполнения, но вычислительно интенсивным задачам.

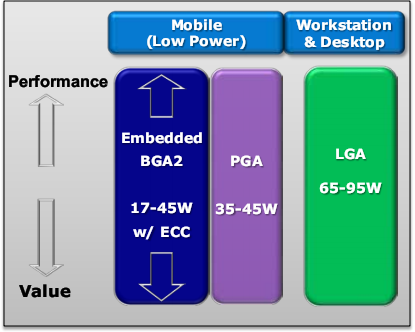

Процессоры будут поставляться с широким диапазоном значений TDP и частот в разных (не совместимых с современными) корпусах для новых материнских плат. Для десктопов это LGA1155 (частоты 2,3–3,4 ГГц), а для мобильных ПК — PGA и BGA2 (2,2–2,7 ГГц). В чипсетах 60-й серии (которые представляют собой, как и их предшественники, только южный мост) появится поддержка SATA-III (с удвоенной до 6 Гбит/с скоростью), но ещё не будет USB 3.0. Не будет там и системного тактового генератора, перекочевавшего в южный мост, — это означает, что существенный разгон через базовую частоту, зафиксированную на значении 100 МГц, возможен лишь при наличии внешнего генератора, чего на дешёвых платах не будет. Однако Intel оставляет возможность разгона за счёт множителя, который будет разблокирован в моделях с буквой K и может достигать значения 57. Кстати о моделях — их названия так и останутся в виде Core i3/i5/i7, но номер модели теперь 4-значный. Помимо буквы K, его может дополнять S (низкий TDP), T (ещё более экономный) или M (мобильный). Чуть позже выйдут серверные и бюджетные варианты.

Что в итоге? Intel серьёзно обновила Nehalem — без революционных прорывов, а просто последовательно обновляя детали микроархитектуры и внедряя все нововведения последних двух лет. В результате мы в очередной раз должны получить ещё более быстрые, но остающиеся в тех же тепловых рамках процессоры. Используя AVX-оптимизации, Sandy Bridge обещает работать почти вдвое быстрее, чем Nehalem, но и без этого остальные новшества не заставят скучать в ожидании. Что мы, разумеется, проверим.

Для интересующихся картина получится куда более любопытной, если детально исследовать «песчаный мост», сравнить его с главным конкурентом — выходящими на 8-10 месяцев позже процессорами AMD архитектуры Bulldozer — и обнаружить массу как неожиданных совпадений, так и кардинальных различий. Ждите наши новые обзоры!