Играть по чужим правилам трудно — эта истина, очевидно, известна компании AMD как никому другому. Можно ли стать лидером или хотя бы рассчитывать на паритет, копируя чужую архитектуру, расширения для нее и т.п.? То есть в каждый момент времени, осваивая то, что для «первоисточника» уже является пройденным этапом? Ответ очевидный. Но так уж повелось, что альтернативные (а уж тем более — несовместимые) решения на массовом процессорном рынке приживаются плохо, и тому есть общеизвестные объективные причины. Получается, что для изменения ситуации в свою пользу мало ввести свои правила, надо еще и заставить играть по ним конкурентов! А это, согласитесь, не просто, в особенности, если основной конкурент может поддержать «свое» видение мира ЦП на порядок более круглой суммой.

Трудно сказать, какие цели в качестве программы-максимум ставила сама AMD на момент анонса архитектуры AMD64, впервые решившись ввести свои «правила игры» (вместо того чтобы ждать, положенных по сценарию, прав на копирование IA-64). Но факты на сегодня вполне однозначны — предложения AMD не только одобрены отраслью, но и впервые массово копируются конкурентом. Это касается и самой AMD64 и мелочей вроде «антивирусного» NX-bit и динамического управления частотой и напряжением питания (Cool&Quiet). А объявление Intel об отказе от использования архитектуры NetBurst в следующем поколении процессорных ядер и возврату к «короткоконвейерному» ядру и вовсе — натуральный подарок ко второй годовщине выпуска Athlon 64.

Не слишком ли категоричное заявление? Возможно. Но лишь — на самую малость :). Именно Athlon 64 продемонстрировал, что у процессоров с коротким конвейером есть отчетливые перспективы в качестве универсальных («настольных», а не только мобильных). И соотношение производительность/тепловыделение стало предметом претензий к нынешним Pentium 4 / Pentium D тоже не само по себе, а в сравнении с все теми же 64-ми. То есть, как минимум, доля вины этого процессора в смене курса Intel, имеется. Но почему подарок? Ведь одним аргументом в пользу процессоров AMD, той самой разницей в тепловыделении, через год станет меньше?

Архитектуру — архитекторам, технологию — технологам!

Разумеется, никто и не сомневался, что Intel предпримет некие меры для устранения возникших диспропорций. Более того, лучшего момента для анонса чего-то принципиально нового (если таковое имеется в распоряжении инженеров Intel), и придумать трудно. Если не сейчас, то — когда? Но громкой сенсации не состоялось, избранный вариант с возвратом к местами обновленной, но, по сути, прежней архитектуре — наиболее предсказуем по последствиям из всех возможных.

Поскольку когда архитектуры у конкурирующих процессоров примерно одинаковы, качественную разницу в производительности будут обеспечивать, уж извините за каламбур, количественные параметры (тактовые частоты, объем кэшей и т. п.). Кое-какие различия, конечно, сохранятся, их можно будет анализировать в свое удовольствие, находить разницу в синтетических тестах, реальных приложениях из категории «особо чувствительных» и «рекламно-оптимизированных» с учетом особенностей одной архитектуры при полном игнорировании другой (последнее, к счастью, уже давно можно встретить лишь в технодемках, выпускаемых самими чипмейкерами). Но разброс результатов в следующем поколении процессоров будет меньше, нежели у равнорейтинговых Pentium 4 и Athlon 64 образца 2003–2005 годов.

Не исключено, что, имея обкатанное ядро, AMD сможет в такой ситуации сохранить позиции, вообще ничего не предпринимая. Тем не менее, повышение частот, вне зависимости от конъюнктуры рынка, запланировано еще до перехода на 65 нм техпроцесс, и мало кто удивится, если «взятие» очередной частотной ступеньки состоится даже для текущей ревизии процессорных ядер, в том числе — двухъядерных. Поддержка интегрированным контроллером памяти DDR2-667, также подсыплет некоторое количество тридэ- и прочих «марок» в копилку Athlon 64 образца 2006 года. Технология виртуализации ресурсов Pacifica и безопасности Presidio также будут предметом для сравнения с Vanderpool и LaGrande от Intel, соответственно (и, определенно, заслуживают отдельной статьи). Но все это — в «высоком классе» дорогих моделей.

Что касается бюджетного сегмента, нынешние Athlon 64 для Socket 939 в новом окружении будут чувствовать себя, по меньшей мере, не хуже, чем сейчас — процессоры для Socket 754. Их производительность достаточно высока, тепловыделение — умеренное. В то время как позиции Pentium 4 и Pentium D с архитектурой Netburst, после выпуска «коротко-конвейерных» процессоров от самой Intel, существенно отличающихся по потребительским свойствам (судя по информации с того же IDF, где новое поколение на всех слайдах сравнивалось с нынешним), могут существенно пострадать. Возможно, Intel потребуется форсировать обновление модельного ряда. В противном случае, в выигрыше окажется тот… кто сможет в массовых количествах предложить процессоры с ожидаемыми общественностью потребительскими свойствами.

Ориентировочный roadmap настольных процессоров AMD

2005 год 90 нм SOI+DSL | 2006 год (первый квартал) 90 нм SOI+ DSL | 2006 год (второй квартал) 90 нм SOI+DSL | конец 2006 — 2007 год 65 нм SOI+DSL | |

| Athlon 64 X2 | Toledo (Socket 939, Dual Core, 2 × 1MB L2, SSE3, DDR400) 4400+ (2,2 ГГц) 4800+ (2,4 ГГц) | Toledo (Socket 939, Dual Core, 2 × 1MB L2, SSE3, DDR400) 4000+ (2,0 ГГц) 5000+ (2,6 ГГц) | Windsor (Socket M2, Dual Core, 2 × 1MB L2, DDR2 667, SSE3, Pacifica, Presidio) | ? (Socket M2, Dual Core, 2 × 1MB L2, DDR2 667, SSE3, Pacifica, Presidio), постепенный перевод существующих моделей на 65 нм |

Manchester (Socket 939, Dual Core, 2 × 512KB L2, SSE3, DDR400) 3800+ (2,0 ГГц) 4200+ (2,2 ГГц) 4600+ (2,4 ГГц) | ? (Socket M2, Dual Core, 2 × 512KB L2, DDR2 667, SSE3, Pacifica, Presidio) | |||

| Athlon 64 FX | San Diego (Socket 939, 1MB L2, SSE3, DDR400) FX-55 (2,6 ГГц) FX-57 (2,8 ГГц) | San Diego (Socket 939, 1MB L2, SSE3, DDR400) FX-59 (3,0 ГГц) | Orleans (Socket M2, 1MB L2, DDR2 667, SSE3, Pacifica, Presidio) | |

| Athlon 64 | San Diego (Socket 939, 1MB L2, SSE3, DDR400) 3700+ (2,2 ГГц) 4000+ (2,4 ГГц) | Orleans (Socket M2, 1MB/512KB L2, DDR2 667, SSE3, Pacifica, Presidio) < 4200+ | ? (Socket M2, 1MB/512KB L2, DDR2 667, SSE3, Pacifica, Presidio) < 4200+ | |

Venice (Socket 939, 512KB L2, SSE3, DDR400)3000+ (1,8 ГГц) — 3800+ (2,4 ГГц) | ||||

| Sempron | Palermo (Socket 939, 128KB L2, 64bit, SSE3, DDR400) 3400+ (2,0 ГГц) | Palermo (Socket 939, 256KB L2, 64bit, SSE3, DDR400) 3500+ (2,0 ГГц) | Palermo (Socket 939, 128/256KB L2, 64bit, SSE3, DDR400) 3700+, 3800+ (2,2 ГГц) | Manila (Socket M2, 128/256KB L2, 64 bit, SSE3, DDR2 667) |

Palermo (Socket 754, 128/256KB L2, 64 bit, SSE3, DDR400) 2600+ (1,6 ГГц) — 3400+ (2,0 ГГц) | Palermo (Socket 754, 128KB L2, 64 bit, SSE3, DDR400) 3600+ (2,2 ГГц) | Palermo (Socket 754, 256KB L2, 64 bit, SSE3, DDR400) 3700+ (2,2 ГГц) |

А дальнейший прогресс будет определяться вторым (наравне с архитектурой) фактором успеха микропроцессорного бизнеса — технологическим процессом. Причем в отличие от архитектуры, унификация техпроцессов AMD и Intel, по крайней мере, на протяжении ближайших двух-трех поколений, точно не состоится.

Так было не всегда, во времена 0,25 мкм технологий на конвейере Intel вполне можно было бы выпускать процессоры AMD и наоборот. Окончательно же разошлись дорожки как раз когда Intel начала экспериментировать с архитектурой Netburst. А вся «остальная отрасль» во главе с IBM при деятельном участии AMD, Freescale, Infineon, Motorolla, Soitec, Sony, STMicroelectronics, TSMC, Philips и еще доброй сотни (!) разной степени известности компаний, активно взаимодействуя друг с другом, с тех пор занималась поиском технологий так или иначе связанных с разгоном «традиционных» процессоров. То есть микросхем, чьи логические схемы разрабатываются для решения неких пользовательских алгоритмов с максимальной эффективностью, без попытки достичь каких-либо искусственно поставленных целей (например, достижение высокого значения тактовой частоты в гигагерцах, актуального в эпоху лозунга «продаются мегагерцы»). Повышение производительности таких микросхем, включая и рост тактовой частоты, обеспечивается не столько логическими изменениями (хотя и они, конечно, имеют место), сколько совершенствованием технологии производства.

Представители AMD неоднократно признавали, что Opteron и Athlon 64 обязаны своей привлекательностью техпроцессу в не меньшей степени, чем конструктивным особенностям. Частотный потенциал без использования всего пакета технологий (в первую очередь SOI), даже на 90 нм едва ли превысил бы 2,0–2,2 ГГц, а двухъядерники можно было бы даже не трудиться выпускать. Очевидно, что ни интегрированный контроллер памяти, ни поддержка Hyper-Transport и 64-битного расширения в таком случае не сделали бы процессор конкурентоспособным на серверном и десктопном рынках.

Даже далекие от ИТ-отрасли как таковой, потребители компьютерного «железа» уже привыкли следить за сменой нанометров в характеристиках техпроцесса, и уверены, что «мельчание» должно приводить к расширению частотного потенциала и снижению тепловыделения. В общем случае, так оно и есть, но в последнее время эти ожидания оправдываются не всегда. И есть ощущение, что AMD, как завзятый борец со штампами (помните: «частота — не главное»?) следующей своей мантрой намерена избрать что-то вроде «не важно СКОЛЬКО нанометров, важно КАКОЙ техпроцесс». Возможно, не в такой категоричной форме, поскольку противопоставлять одну (и важную) характеристику другим все же некорректно.

Ситуация для привлечения внимания к технологическим особенностям сейчас благоприятная — чем «мельче» становится техпроцесс, тем большее влияние на результат его внедрения оказывают легирующие технологии. Пожалуй, самая «интуитивно понятная» проблема (и одновременно признанная наиболее серьезной), сопутствующая уменьшению размеров базовых элементов микросхем — возрастание токов утечки. Пропорционально уменьшению размеров элементов, уменьшаются и формирующие их слои, так слой изолятора, оксидной пленки, уже по нормам 90 нм техпроцесса составляет 1,2 нм (5 атомных слоев). Именно через этот барьер просачивается ток, являющийся на сегодня основным нарушителем тепло-экономических показателей микросхем. В результате переход на уменьшенный техпроцесс по-прежнему успешно решает задачу повышения скорости переключения транзисторов, а вот уровень тепловыделения «автоматически» не снижается. Косвенно повлиять на токи утечки можно, меняя материалы изолирующих слоев. Но пригодные к массовому применению заменители традиционного оксида кремния (так называемые, High-k диэлектрики) появятся, самое раннее, ко времени готовности 45 нм техпроцессов.

Атомарный масштаб элементов в сочетании с низкими пороговыми уровнями напряжения грозит еще одним (по ряду оценок вторым по значимости после токов утечки) явлением — «мягким отказам». Упрощенно говоря, превратить «ноль» в «единицу» становится по силам, даже оторвавшимся от упаковки микросхемы альфа-частицам, и уж тем более частицам, «прилетевшим» из космоса. Мягкие отказы неприятны тем, что могут периодически возникать в исправных микросхемах и непредсказуемо искажать информацию. Отбраковать продукцию, склонную к таким дефектам, на этапе тестирования, скорее всего, не удастся. По той причине, что в тестах, даже если мы будем проводить их в условиях, искусственно приближенных к «космическим», исправная работа отдельно взятой микросхемы не сможет послужить критерием годности (и обратное тоже верно). Включается слишком много случайных факторов и фактически можно говорить лишь о сборе статистики вероятности возникновения мягких отказов на основе длительного тестирования (сопоставимого с самим сроком службы микросхемы). А снизить эту вероятность могут лишь защитные меры на этапе проектирования — причем как на логическом уровне (выявление и коррекция ошибок), так и технологические, в частности, использование «обедненных» материалов для упаковки микросхем.

Между тем, давно существует, а за последние несколько лет доросла и до массового производства, технология, позволяющая решить обе перечисленные проблемы, причем достаточно радикальным образом.

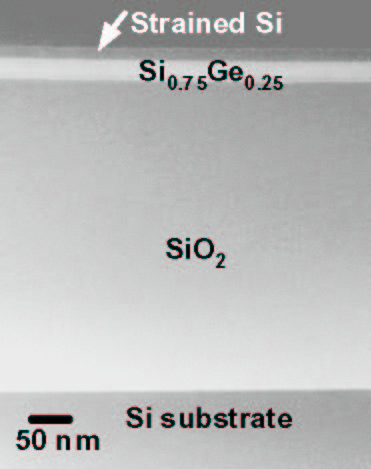

Как нетрудно догадаться, это и есть упомянутая SOI — «кремний-на-изоляторе», технология в буквальной интерпретации своего названия предполагает нанесение дополнительного слоя кристаллического кремния (Top Silicon на картинке) поверх той самой «истончающейся» оксидной пленки (изолятора).

В результате образуется еще один слой надежного изолятора, препятствующий утечке тока и создающий барьер, в том числе, и против «космических» частиц. Едва ли нужно представлять эту технологию «по форме», она появилась давно и обсуждалась в деталях (для знакомства с основами полупроводникового производства см. например, вот эту статью). Сосредоточимся на истории ее использования в процессорах AMD.

Урожай SOI

Вопреки распространенному мнению, AMD обратила внимание на эту технологию не под влиянием своего технологического партнера и одновременно главного идеолога SOI — компании IBM. Началась история в ноябре 2001 года (на тот момент в партнерах по шлифовке техпроцессов AMD значилась Motorola), когда был подписан контракт с французской компанией Soiteс, изготовителем субстрата, кремниевых пластин, располагающей более совершенной технологией производства SOI-пластин по сравнению с IBM. В техпроцессе IBM кремниевая пластина бомбардируется ионами кислорода, они проникают на заданную глубину и формируют оксидный слой, поверх которого остается слой чистого кремния. Тогда как по методу Soitec, оксидная пленка формируется на поверхности кремниевой подложки традиционным способом, а поверх нее прикрепляется… еще одна «подложка». Излишек кремния с поверхности последней снимается остроумным способом, получившим имя собственное — SmartCut. Здесь также используются разогнанные ионы (водорода), проникающие на заданную глубину и формирующие плоскость разрыва. Лишний материал отслаивается по этой плоскости, после чего пластину шлифуют. Себестоимость такого техпроцесса ниже, и он лучше подходит для условий массового производства.

Пролетая над Soitec (г. Бернин, Франция) в момент пуска

линии для производства 300-миллиметровых пластин :)

С тех пор мало что изменилось, AMD сотрудничает в разработке технологических процессов с IBM, а SOI-пластины по-прежнему используются от Soiteс. Контракт продлен как раз в начале этого года, так за 2005 год AMD закупит 200 и 300-миллиметровых пластин (последние, естественно, для производства чипов на введенной в строй дрезденской Fab36) больше чем на 50 млн. долларов. Поэтому интересно познакомиться с планами Soiteс, тем более, что они оформлены до 2011 года, когда на поверхности изолятора планируется формировать слой германия вместо кремния.

Текущее состояние разработок связано с интеграцией напряженного кремния с технологией SOI. Технология уже используется в массовом производстве, а подробнее мы этой темы коснемся ниже.

А здесь осталось только кратко обосновать, почему же Intel не стал применять эту технологию, если ее преимущества столь явны? Во-первых, на момент принятия решения, они не были настолько очевидны. Фактически SOI первоначально рассматривался, как один из способов снизить паразитную емкость и поднять скорость переключения транзисторов. Это действительно так, но в Intel посчитали, что прирост производительности от реализации SOI будет меньше — 13 % вместо 20–35 % (по версии IBM), причем работать этот метод будет со все меньшей эффективностью по мере уменьшения технологических норм, так уже для 0,13 мкм ожидалось лишь 8 %. Более дорогие пластины — делался вывод — сведут общий результат к отрицательному. Что касается токов утечки через изолятор, они не были так актуальны во времена техпроцессов с нормами больше 0,13 мкм.

Возможно ли появление SOI в техпроцессах Intel в обозримом будущем? Маловероятно. Особенно если Intel удастся ввести давно обещанный «проприетарный» High-k-диэлектрик вместо оксида кремния в 45 нм техпроцессе, который должен вернуть токи утечки в приемлемые границы. А SOI, хоть и оказалась успешно стыкуемой с другими технологиями, вроде «напряженного кремния». И, возможно, ее удастся при необходимости скомбинировать и с High-k-диэлектриками (благо времени для этого предостаточно, SOI будет противостоять токам утечки «сама по себе» еще долго и потребность в таком сочетании появится не раньше 32 нм техпроцесса). Но задачи эти далеко не тривиальные и времяемкие даже для компаний «от роду» связанных с SOI, с ходу их нельзя решить.

Напряженный кремний

Как и в случае с SOI, AMD задумалась над использованием напряженного кремния (Strained Silicon), не вчера, а также до начала сотрудничества с IBM. Эпизод был связан с именем компании AmberWave (редко упоминаемой в новостях, если не считать поданного ею этим летом иска… против Intel в использовании запатентованной ею технологии растягивания кристаллической решетки кремния с использованием кремний-германиевого соединения). Однако «тогда» ничего пригодного для реализации в массовом производстве не получилось. Зато отлично получилось сейчас.

Особенностью технологии напряженного кремния (Strained Silicon) в исполнении AMD и IBM, получившей название DSL — Dual Stress Liner является использование нитрида кремния с измененной кристаллической решеткой в обоих случаях — для растяжения кристаллической решетки с целью свободного протекания электронов (для NMOS-транзисторов с электронной проводимостью) и сжатия — для облегчения движения «дырок» в PMOS-транзисторах с дырочной проводимостью. Тогда как в техпроцессах Intel нитрид кремния используется только для сжатия решетки для PMOS-транзисторов, а для растяжения — используется промежуточный слой «расслабленного» SiGe-субстрата. Использование германия для подобных целей имеет очень давнюю историю, и в качестве примера изучается в школьном курсе физики — поскольку атомы германия больше атомов кремния, последние «разбегаются» на соответствующие расстояния (таким образом, AmberWave будет не так просто доказать свою правоту).

Унификация методов сжатия и растяжения привела, во-первых, к удешевлению техпроцесса, нитрид кремния использовался и прежде, в пассивном качестве предохраняющей маски на транзисторах. Соответственно, введение напряженного кремния по версии AMD-IBM не повлияло на себестоимость чипов. Во-вторых, такой метод оказался чуть более эффективным с точки зрения быстродействия.

Нынешние реализации напряженного кремния никак не влияют на уровень потребления энергии и токи утечки. Надо лишь подчеркнуть, что технология DSL применяется сейчас в комбинации с SOI. Более того, наготове лежит и технология SGOI с использованием вспомогательного слоя германиево-кремниевого субстрата поверх изолятора.

Как нетрудно заметить, в таком «бутерброде» препятствовать утечке тока будет еще один вспомогательный слой.

Интересно, что Intel тоже возлагает надежды на «напряженный кремний» и как временное решение проблемы токов утечки (для 65 нм техпроцесса). Идея очевидна — деформируя кристаллическую решетку, можно добиваться изменения ее проводящих или изолирующих свойств. Хотя в таком случае, речь может идти лишь о компромиссе — либо мы стремимся к повышению быстродействия, либо добиваемся «бонуса экономичности». Впрочем, это вполне приемлемо, например, для мобильных процессоров.

Прочие технологии

Разумеется, не одна SOI и «напряженный кремний» помогают решать проблемы миниатюризации и повышения производительности трудно разгоняемых «от природы» чипов с короткоконвейерной архитектурой. В идеале этой цели должны быть подчинены все характеристики техпроцесса. Именно по этой причине AMD, IBM и т. д. всегда стремились максимально быстро внедрять технологии, дополнительно позволяющие поднять быстродействие, поскольку одно лишь уменьшение технологических норм уже давно не давало желаемого разгонного потенциала. Вернее, не оставляло запаса с учетом постоянного усложнения логических схем — увеличения количества транзисторов, происходящего одновременно (если не чаще!), чем успевают сменяться техпроцессы.

Так, например, произошло с заменой алюминиевых соединений на медные, позволившие увеличить производительность (до 40 %) , уменьшить площадь кристалла (а, значит, и снизить себестоимость). Сейчас медь используется всеми без исключения производителями.

Еще один показательный параметр — количество слоев металлизации, увеличение количества слоев позволяют сделать кристалл более компактным, уменьшить длину соединений и, как следствие, снизить задержки распространения сигналов. Вместе с тем усложняется производство за счет появления дополнительных этапов (слои, как известно, наносятся последовательно). Максимальное количество слоев традиционно используется приверженцами «короткоконвейерных» архитектур. Так AMD уже со времен Athlon XP использует 9 слоев (Intel планирует перейти на 8-слойный дизайн в 65-нанометровом техпроцессе).

Одновременно с ростом количества слоев обострилась проблема надежной изоляции металлических проводников. Исконно в этой роли выступало флюоросиликатное стекло с коэффициентом диэлектрической проницаемости k=3,6. Не бог весть, какой показатель, но использование других материалов долгое время упиралось во все ту же проблему их беспроблемного сосуществования с другими материалами, входящими в состав микросхем. Впервые в массовом производстве low-k-диэлектрик (Black Diamond k<3.0 от компании Applied Materials начала использовать как раз AMD в 0,13 мкм Athlon XP.

Сотрудничество с Applied Materials (крупнейшим в мире поставщиком комплектующих и расходных материалов для полупроводниковой промышленности) продолжается до сих пор, эта компания участвует в оснащении Fab36, а на 65-нанометровые кристаллы будет осаждаться уже Black Diamond II с минимальным доступным на сегодня k=2,2–2,5.

45-нанометровое будущее

Основными идеями, над которыми экспериментируют все без исключения компании, ответственные за прогресс полупроводниковой отрасли, является замена оксида кремния в качестве изолятора на материал с более высоким коэффициентом диэлектрической проницаемости — (так называемый High-k диэлектрик) в сочетании с металлическим затвором и использование транзисторов с несколькими затворами.

Идею High-k диэлектриков гораздо проще объяснить «на пальцах», чем реализовать на практике. Материал с высокой диэлектрической проницаемостью может быть нанесен более толстым слоем по сравнению с традиционным оксидом кремния без отрицательных последствий для характеристик транзистора, и при этом, благодаря увеличенной толщине, надежно изолировать от токов утечки. Но, увы, это хорошо звучит лишь в теории, на практике наибольшую совместимость с традиционными материалами на сегодня демонстрирует оксид гафния, но и применение этого (достаточно редкого и дорогого) материала тоже под вопросом, точнее — пока невозможно вовсе. Проблемы возникают как в процессе совмещения нового материала с традиционными полупроводниковыми средами (в первую очередь с затвором из поликристаллического кремния, для которого, скорее всего, придется использовать другие материалы, очевидно — металлы). Вторая проблема — электрон-фононные взаимодействия (описательно можно сказать, что электроны, протекающие в канале транзистора, «затормаживаются» таким диэлектриком, имеющим высокую проницаемость).

И хотя переход на High-k диэлектрики некогда планировался уже в 65 нм техпроцессах, в последнее время многие эксперты сходятся на том, что и в 45 нм технологии, возможно, придется обойтись традиционными материалами. По крайней мере, стоит подумать о других вариантах развития.

Остается надежда на реализацию этого способа Intel, которая заявляла о существовании в ее распоряжении некоего материала, успешно прошедшего тесты и успевающего для внедрения в 45 нм техпроцесс. Но никаких подробностей и доказательств до сих пор не представлено. Более того, Paolo A. Gargini, директор технологической стратегии Intel (Director of Technology Strategy), уже высказывался в отношении того, что инженеры компании ищут способ отложить введение High-k диэлектриков до 32 нм техпроцесса. Не исключено, что альтернативой окажется некий вариант многозатворного транзистора (это уже по словам Mark Bohr, ныне директора с труднопереводимой на русский язык позицией (director of Process Architecture and Integration), но подробностей также нет. Тем не менее, в существующем на сегодня официальном «роадмапе» техпроцессов введение многозатворных транзисторов по-прежнему соответствует 32 нм (с пометкой «Research», то есть речь пока идет не о проработке деталей, а о принципиальных проблемах выбора конфигурации и материалов), в то время как High-k по-прежнему числится краеугольной опцией 45 нм техпроцесса. Словом, поживем — увидим, тем более, что даже со всеми мыслимыми задержками, 45 нм техпроцесс мы наверняка увидим в товарных образцах до конца первой декады XXI века.

Каким видит 45-нанометровое будущее AMD? Прототип транзисторной ячейки соответствующего типоразмера был продемонстрирован в 2003 году, тогда же было объявлено, что реализация не зависит от готовности к массовому внедрению High-k диэлектриков, хотя и, разумеется, не исключает его использования в целях дальнейшего подъема скорости работы. В основу положен принцип многозатворного транзистора, который позволяет отказаться от традиционного способа повышения рабочего тока в транзисторах (путем уменьшения толщины все того же многострадального изолятора, что, как уже отмечалось, и сейчас проблематично из-за возрастающих токов утечки в выключенном состоянии транзистора). Очевидно, если мы используем несколько затворов, рабочий ток через них суммируется, и значительно возрастает, даже если мы оставим слой изолятора прежней толщины (именно поэтому можно будет подождать с заменой оксида кремния на High-k-диэлектрик, если последний не «вызреет» ко времени). Для еще большего усиления рабочего тока в качестве материала затвора в AMD предполагают использовать силицид никеля (то есть металл вместо обычного поликристаллического кремния). Оригинальность метода заключается в том, что силицид никеля получается «на месте» из уже выращенного поликристаллического затвора с помощью химического соединения никеля с кремнием.

Скорость переключения получившегося транзистора составляет 0,26 пикосекунд для NMOS и 0,45 пс для PMOS, показатели более чем достойные. А главным ноу-хау и достоинством метода является относительная компактность трехзатворного транзистора от AMD по сравнению с другими существующими на сегодня разработками в этой области. Любой многозатворный транзистор получается объемным, например, в данном случае, затворы располагаются вокруг вертикального канала. И именно это принципиальное усложнение конфигурации, создает основную проблему для литографического оборудования с ограниченной на сегодня глубиной резкости, не приспособленной для работы с рельефными структурами. Именно поэтому введение многозатворных транзисторов всегда связывали с развитием литографического оборудования. Очевидно, в AMD поработали именно над тем, чтобы сделать сам транзистор «достаточно плоским».

Также в 45-нанометровом техпроцессе будет использоваться усовершенствованная технология SOI (так называемая — полностью обедненная) и локально напряженный кремний (разряжение и сжатие будет создаваться непосредственно в областях, через которые протекает «нужный» ток).Резюме

Итоги в прогнозистской статье подводить, разумеется, было бы верхом самонадеянности. Разумеется, каждая из компаний, упомянутых (и подразумеваемых) выше, может преподнести нам сколько угодно не значащихся в официальных планах, сюрпризов. Как приятных, так и не очень. На сегодня можно говорить лишь о нескольких тенденциях, которые ожидают нас в ближайшем будущем:

- Новый раунд будет любопытен тем, что мы будем наблюдать соревнование между дальнейшим развитием идей архитектуры P6 в исполнении Intel и… дальнейшим развитием идей того же самого P6 в исполнении AMD (как известно, корнями архитектуры K7 и K8 глубоко уходят в ту же самую известную почву)

- Качественные различия в производительности будут определяться уже почти только количественными параметрами (тактовой частотой) и способностью эффективно «кормить» процессорное ядро данными (то есть объемом кэш-памяти, ПС системной шины, частотой и латентностью контроллера памяти и т. п.) И лишь во вторую очередь, архитектурными нюансами.

- В свою очередь, для того чтобы обеспечить упаковку адекватного количества транзисторов в чип, работающий с частотой «не хуже, чем у конкурента», придется выжимать все имеющиеся возможности из имеющегося техпроцесса. Для AMD это занятие уже привычно и освоено (курьезный, но отменно работоспособный пример — 130 нм техпроцесс с SOI и напряженным кремнием в «старой версии» Athlon 64 FX-55). Intel, не будем лукавить, до сих пор, имела возможность «хватать по верхам», стараясь как можно быстрее перейти на очередной, более мелкий техпроцесс, без особых усилий по «отжатию соков» из предыдущего. Отчасти это провоцировалось самой архитектурой Netburst, в эпоху расцвета хорошо «разгонявшейся» и без особых технологических уловок. Что будет дальше? Посмотрим.

Влияние различных методов совершенствования техпроцессов на потребительские свойства микросхем

| Уменьшение проектных норм | Увеличение количества слоев металлизации | Медные соединения вместо алюминиевых | Low-k диэлектрик для изоляции межтранзисторных соединений | Кремний на изоляторе (SOI) | Напряженный кремний (Strained Silicon) | High-k диэлектрик в качестве материала изолятора в транзисторах | Многозатворные транзисторы (Multi Gates) | |

| Скорость переключения транзисторов (частотный потенциал) | повышается | снижаются задержки распространения сигналов в пределах микросхемы | повышается (40 %) | повышается (20–40%) | повышается (20–35 %) | Повышается (15–20 % по версии Intel, 24 % — AMD, IBM) | исследуется (возможно ухудшение отдельных характеристик, связанных с производительностью) | повышается |

| Энергопотребление и тепловыделение | снижается (степень снижения определяется успешностью решения сопутствующих технологических проблем) | зависит от конкретной реализации | снижается | снижается за счет снижения тока утечки между слоями металлизации | снижается за счет снижения тока утечки транзистора в выключенном состоянии | не меняется | снижается | снижается |

| Сопутствующие технологические проблемы | множество, на данный момент наиболее критичным считается увеличение тока утечки через «истончающийся» слой диэлектрика | усложняется проектирование, отладка и производство, растет число этапов формирования кристалла | на данный момент решены (создание электрического контакта меди и кремния, в результате обернулись преимуществами — отпала необходимость в планаризации слоев) | нет, но продолжается поиск материалов с еще более низким коэффициентом диэлектрической проницаемости | на данный момент решены (получение надежного контакта слоя кремния с изолирующей пленкой) | реализована только «первая очередь» этой технологии, в дальнейшем обещан творческий подход к деформации кристаллической решетки | находится на стадии разработки | находится на стадии разработки |

| Себестоимость готовых чипов | снижается | Зависит от конкретной реализации. Как правило, снижается благодаря существенному уменьшению площади кристалла | снижается | повышается | повышается (первоначально около 10 %) | практически не меняется | повышается | повышается (требуется усовершенствование литографического оборудования для формирования объемных структур) |

| Кем используется | всеми | Athlon XP и 64 содержат 9 слоев, Pentium 4, ядро Prescott — 7 слоев | IBM с 1998 года, AMD с 2000, Intel с 2002,в настоящее время — для всех техпроцессов с нормами от 0,13 мкм и меньше используются медные соединения | Диэлектрики с k<3.6 используются в настоящее время всеми компаниями, производящими как центральные, так и графические процессоры | IBM с 1999 года (линейка PowerPC), AMD с 2003 года (Opteron, Athlon 64) | с 2004 года Intel (90 нм Pentium 4, Pentium D), AMD (130 нм Athlon 64 FX55, 90 нм Athlon 64 Venice и San Diego, Athlon 64 X2) | 2007–2008 год (?) Intel (45 нм) | 2007–2008 год (?) AMD, IBM (45 нм) |

Ссылки по теме:

- AMD & Silicon-on-Insulator Special

- Strained-Si-on-Insulator (SSOI) and SiGe-on-Insulator (SGOI): Fabrication Obstacles and Solutions

- Intel Corp. and IBM Microelectronics clashed over the benefits of silicon-on-insulator (SOI) technology

- IBM — старый новый партнер AMD в разработке техпроцессов

- low-k dielectrics for high-volume production in AMD Opteron and AMD Athlon 64