Подсистемы памяти персональных компьютеров прогрессируют с высокой скоростью – достаточно вспомнить, сколько раз менялись гнезда для установки модулей памяти на системных платах. Каждый раз для перехода на новую технологию были веские причины – рос объем и быстродействие оперативной памяти, сокращалось время доступа к ней. Было бы ошибкой думать, что однокристальные системы (system-on-chip, SoC) остаются в стороне от технического прогресса – ярким примером обратного может служить разработка компании Sonics, являющейся одним из поставщиков решений для однокристальных систем.

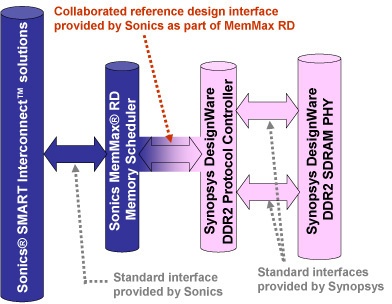

Компания представила MemMax RD, новую версию так называемого планировщика – блока, реализующего важную функциональную часть контроллера памяти. Планировщик имеет интерфейс для непосредственного сопряжения с контроллером протокола Synopsys DesignWare DDR2 SDRAM (и в том, и в другом случае речь идет о продуктах интеллектуальной собственности – IP). Объединив MemMax RD и DesignWare DDR2 SDRAM Protocol Controller IP, разработчики получают готовое решение, обеспечивающее пропускную способность более 5 Гб/с при утилизации канала 80% и соблюдении требований Quality of Service (QoS), необходимых при работе, например, с потоковым видео высокой четкости.

В настоящее время стандартом де-факто становится многоядерная архитектура SoC. Вследствие конвергенции, свойственной современной портативной электронике, сложность однокристальных систем растет день ото дня. В свою очередь, это повышает требования к средствам, организующим потоки информации внутри SoC. Среди них можно выделить механизмы, обеспечивающие арбитраж доступа к памяти по внутренней шине SoC или в рамках системы более высокого уровня, включающей подсистему внешней памяти. Одним из ключевых, в этих условиях, становится требование обеспечения QoS при совместном использовании общего канала обмена с внешней памятью и сохранении высокой степени утилизации (загрузки) канала. Утилизация канала, определяемая, как доля тактов синхронизации SDRAM, в течение которых выполняется фактическая пересылка данных, задает тип, частоту и конфигурацию внешних компонентов DRAM, которые необходимы для достижения запланированного уровня производительности.

Источник: Sonics