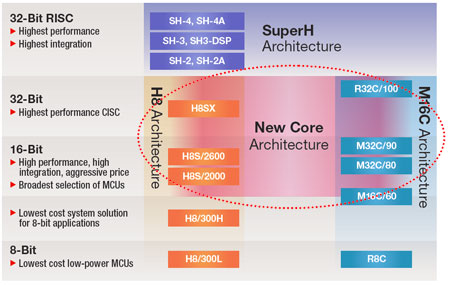

Речь идет об архитектуре, предназначенной для 16- и 32-разрядных микроконтроллеров нового поколения, которая объединит преимущества существующих ядер H8 и M16C с современными разработками.

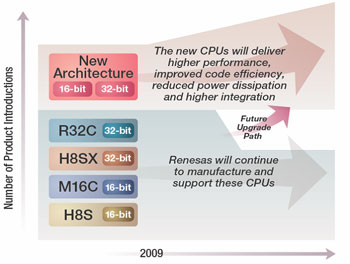

Являясь преемниками 16-разрядных CPU M16C и H8S, и 32-разрядных CPU R32C и H8SX, новинки будут совместимы с ними по набору команд, периферийных регистров и инструментарию разработчика. Среди приоритетов, обозначенных перед началом разработки, Renesas Technology называет эффективность кода (показатель компактности программ – более эффективный код требует меньше памяти), производительность (количество операций в единицу времени и тактовая частота) и энергопотребление.

Цель, поставленную Renesas, скоромной не назовешь – решено создать лучшие в мире процессорные ядра по совокупности свойств: эффективности кода, производительности, энергетической эффективности и цене. В частности, предполагается, что применение новой архитектуры позволит уменьшить размеры программ на 30%, а энергопотребление CPU на 50%.

Как ожидается, спецификации новых CPU будут обнародованы в начале 2008 года, а первые приборы на их базе появятся на рынке во втором квартале 2009 года. Для производства предполагается задействовать 90-нм техпроцесс.

Источник: Renesas Technology