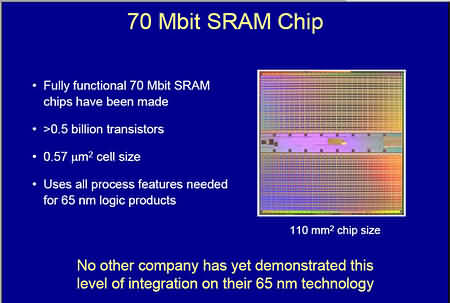

Как сообщает японское представительство Intel официальным пресс-релизом, на фабрике в Орегоне компания выпустила образец 70 Мбит SRAM, выполненный с использованием норм 65-нм техпроцесса по технологии «напряженного кремния, strained silicon». Напомним, что это – не первый чип памяти, выпущенный компанией по такой технологии: в ноябре 2003 года Intel выпустила 4 Мбит чип (площадь ячейки – 0,57 мкм2).

Размер ячейки памяти нового чипа – такой же, как у 4 Мбит предшественника; чип имеет более 0,5 млрд. транзисторов. Длина затвора транзистора – 35 нм, что примерно на треть меньше размера затвора транзистора кристалла, выполненного с использованием норм 90-нм техпроцесса. Кроме того, как отмечается в пресс-релизе, разработчик сумел сократить токи утечки – примерно в 4 раза по сравнению с чипами, выполненными по обычной технологии.

Основной упор в пресс-релизе компании сделан на пониженное энергопотребление – сократить его позволило внедрение так называемых «спящих транзисторов» (sleep transistor), основная функция которых сводится к отключению незадействованных цепей. В пресс-релизе отмечено, что серийное производство чипов, выполненных с использованием норм 65-нм техпроцесса, ожидается в первой половине 2005 года – технология будет внедрена последовательно на орегонской, аризонской фабриках компании, а потом – и на производственных линиях в Ирландии. Как отметили представители Intel, компания постарается снизить капзатраты на производство за счет использования существующего литографического оборудования (248 и 193 нм).