Канадская исследовательская фирма Chipworks встала на защиту корпорации Sony, сообщив, что по ее мнению, процессор EE+GS для игровой приставки PlayStation X действительно выполнен по 90-нм нормам. Напомним, что в понедельник Semiconductor Insights высказала сомнения в том, что чип действительно выполнен по 90-нм технологии, а не по нормам 130 нм.

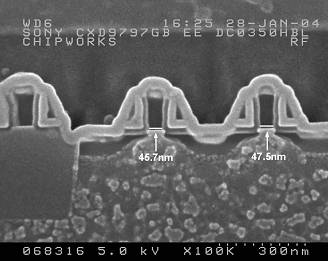

Таким образом, мнения разных аналитиков разделились: Chipworks сообщает, что измеренная ими длина затвора транзисторов EE+GS составляет 45-50 нм, что удовлетворяет 90-нм нормам, в то время как Semiconductor Insights настаивает на том, что минимальная длина затвора составляет 70 нм, что соответствует нормам 130 нм. Chipworks отмечает, что чип Sony/Toshiba немного отличается от того, что требуется согласно спецификациям ITRS (International Technology Roadmap for Semiconductor), опубликованным в этом году – для того, чтобы считать чип соответствующим 90-нм нормам там рекомендуется длина затвора в 37 нм. Однако технологический процесс Sony и Toshiba соответствует результатам выпуска пилотных 90-нм чипов Intel, представленных на IDF.

Тем не менее, результаты «вскрытия», представленные Chipworks, не убедили Semiconductor Insights в правоте слов Sony, хотя, к чести обеих компаний, в подлинности обоих измерений никто не сомневается. По словам Эдварда Кейса (Edward Keyes), главного технического директора Semiconductor Insights, Sony ранее и не говорила ни разу о том, что длина затвора составляет около 47 нм, а кроме того, наличие в чипе затворов такой длины еще не доказывает того, что все они обладают такими же размерами (хотя и признается, что разброс значений параметров не так уж и велик и определяется особенностями технологического процесса, одинакового для всех частей чипа). По мнению Кейса, он не вправе комментировать полученные Chipworks фотографии, потому что не располагает данными о том, в каком режиме работал сканирующий туннельный микроскоп и нет ли здесь ошибки. Возможно также, что на результаты измерений повлияли особенности «вскрытия» полупроводникового чипа, точнее, того, в какой плоскости был произведен разрез.

Кейс не отрицает того, что размеры затворов подвержены статистическим вариациям. В защиту мнения Semiconductor Insights он привел тот аргумент, что ширина проводника в EE+GS составляет около 260 нм, в то время как по нормам ITRS для 90-нм она должна быть равна 210 нм, а для 130-нм – 295 нм.

В ответ на аргументы Semiconductor Insights, исследователи Chipworks сообщили, что действительно наблюдали часть транзисторов с длиной затвора более 50 нм. Однако настолько большая вариация средней величины, по их мнению, скорее всего, невозможна, по крайней мере, не в процессорном ядре. Однако во встраиваемой DRAM вариации параметров могут быть гораздо существеннее, а так как аналитики не знают, какой части чипа принадлежат исследованные ими транзисторы, это может стать объяснением различий.