CeBIT 2003. VIA Technologies, Inc.

VIA Technologies является одним из лидеров в области построения чипсетов и процессоров, и приходится констатировать, что год от года натиск тайваньского гиганта становится все ощутимее, и другому монстру индустрии, компании Intel, приходится прилагать немалые усилия для удержания прежних позиций, не говоря уже о завоевании новых.

Пресс-конференция VIA, проведенная в Ганновере в дни выставки CeBIT 2003 собрала, пожалуй, самую многочисленную аудиторию, если не брать во внимание конференцию ATI, где небольшого зала попросту не хватило для всех желающих.

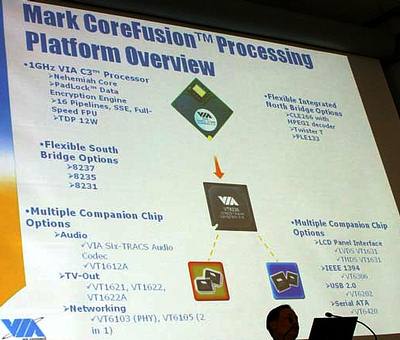

Мы уже сообщали в наших новостях информацию о том, что в этом году VIA начинает работу над совершенно новым процессорным проектом с рабочим названием Mark. О новом проекте, который полностью называется Mark CoreFusion, компания рассказала на конференции в рамках выставки CeBIT 2003.

Основная идея нового чипа Mark CoreFusion — интеграция северного моста в процессор VIA C3. Должно получиться что-то вроде C3 (точнее, ядро Nehemiah) и CLE266 в одном корпусе. Следующий шаг — интеграция в гибридный процессор южного моста, что-то класса VT8235. В прошлом компания уже вынашивала такой проект, тогда на CeBIT 2000 были представлены планы выпуска интегрированного чипа Matthew. Впоследствии проект был заморожен. Впрочем, ничего удивительного в этом нет: по тем временам, навряд ли получилось бы что-нибудь с достаточной производительностью. Кстати, схожий проект от Intel — Timna — и вовсе был отменен.

Почему проект Matthew реанимирован? Все очень просто: нынешнюю мини-платформу компании, EPIA, можно назвать вполне удачным проектом. На конференции представители компании с удовольствием демонстрировали работающие системы и платформы.

Почему бы, решили в компании, не упрочить и не развить успех. По сути, конструктив чипа Mark будет представлять собой гибридную микросхему, в нынешние времена именуемую MCM (Multi Chip on Module). Процессорное ядро и чипсет будут производиться раздельно, интеграция на единую подложку будет производиться уже в соответствии с рыночным спросом на модели с определенной таковой частотой или в соответствии с пожеланиями заказчика. В результате, чип Mark CoreFusion первого поколения будет представлять собой гибрид из 1 ГГц процессора C3 с напряжением на ядре 1,25 В и энергопотреблением уровня 12 Вт, северного моста CLE266 с интегрированной графикой S3 CastleRock и аппаратной поддержкой декодирования MPEG-2, аналоговыми и DVI выходами, SDRAM и DDR SDRAM интерфейсом (DDR266). Возможны варианты с северными мостами PM133/266 (графика Savage4) или PLE133 (графика Trident). В качестве интегрированных вариантов южного моста предполагается использовать как VT8235, так и VT8237.

Разумеется, весь этот «бутерброд» в виде нынешнего прототипа отличается суммарным энергопотреблением, которое на вариант без активного охлаждения никак не вытягивает. Задача компании — привести решение класса Mark CoreFusion к работе с пассивным охлаждением. Особенно подчеркивается, что компания не преследует при разработке чипа Mark достижения каких-либо «скоростных» характеристик.

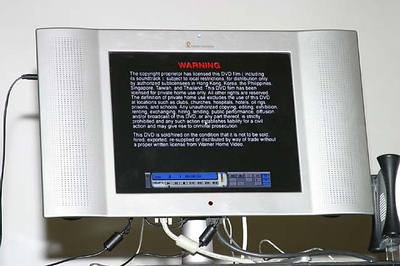

Еще одним важным сообщением компании стал анонс разработки новой миниатюрной платформы Nano ITX, как раз для работы с чипами серии Mark CoreFusion. К сожалению, никаких подробностей о Nano ITX пока нет, кроме как сообщения о том, что размеры таких плат будут меньше форм-фактора mini ITX примерно на 15%. Дело идет к тому, что подобные платформы со временем, по расчетам VIA, будут интегрироваться непосредственно в ЖК-мониторы. Примерно как в этом прототипе:

Также компания продемонстрировала прототип мобильного процессора Mobile C3 с рабочим называнием Antaur.

Mobile C3 Antaur будет изготавливаться на базе ядра Nehemiah с применением производственных норм 0,13 мкм техпроцесса, в 386-контактном корпусе EBGA (Enhanced Ball Grid Array) габаритами 35×35 мм.

|

|

Нынешний прототип обладает тактовой частотой 1,0 ГГц FSB 133 МГц, напряжение питания ядра в полнофункциональном режиме — 1,25 В. В качестве энергосберегающей технологии заявлена VIA PowerSaver 2.0, регулирующая тактовую частоту и напряжение на ядре в зависимости от режима работы.

Совершенно очевидно, что разработка мобильного процессора VIA Antaur и интегрированного чипа VIA Mark ColdFusion, где ядро C3 совмещено в одном корпусе с южным и северным мостом — суть разные грани одного проекта. Более того, по уточненным данным, технология PowerSaver2.0 также является неотъемлемой частью проекта Mark CoreFusion.

Будем надеяться, что в самое ближайшее время VIA приоткроет завесу тайны над этим проектом. В любом случае, теперь становится понятнее, откуда у компании амбициозные планы довести объемы продаж своих процессоров в 2003 году до 6 млн. штук…

На конференции были также представлены серийные ноутбуки, работающие на процессоре C3 и графикой S3.

на котором и писались репортажи с CeBIT 2003

|

|