Продолжают поступать новости с конференции ISSCC. В частности, стало известно о новой разработке компании Renesas Technology: процессоре с массовым параллелизмом, основанном на матричной архитектуре.

Процессор программируемой конфигурации содержит 2048 процессорных элементов и 1 Мбит SRAM. Его производительность составляет 40 GOPS (млрд. операций в секунду) при тактовой частоте 200 МГц. Область применения новинки - работа с мультимедийными данными.

Обработка аудио- и видеоданных чрезвычайно востребована на текущем этапе развития вычислительной техники, особенно в свете растущей популярности развлекательной составляющей систем цифрового дома и портативных мультимедийных устройств. Она включает операции быстрого преобразование Фурье, вычисление свёртки и другие. До настоящего момента, эти операции обычно реализовывались специализированной "жесткой логикой" или цифровыми сигнальными процессорами (digital signal processor, DSP). Между тем, например, рост разрешения изображений требует повышения производительности аппаратных средств, а появление и развитие большого количества форматов представления мультимедиаданных наталкивает на мысль, что использование программируемых процессоров является наиболее оправданным выбором, с учетом обеспечиваемого ими потенциала для расширения.

Один из способов повышения производительности - увеличение тактовой частоты. К сожалению, он поднимает вопросы сохранения тепловыделения на разумном уровне. То же соображение применимо и к процессорам типа MIMD (multiple instruction multiple data - "много потоков команд, много потоков данных").

Архитектура разработки Renesas Technology отличается от архитектуры традиционных процессоров DSP и MIMD. Она обозначена, как "мелкозернистая" SIMD (fine-grained single instruction multiple data - "один поток команд - много потоков данных").

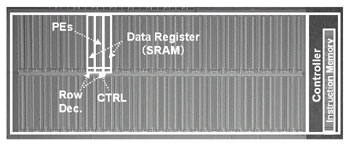

Новинка состоит из 2048 двухразрядных процессорных элементов (processing elements, PE) и 512-разрядной памяти, используемой в качестве регистров данных (в общей сложности - 1 Мбит).

Ключом к повышению производительности является высокоэффективная связь между элементами процессора. Она организована "по горизонтали" (между PE и регистрами) и "по вертикали" (между PE). Матричная структура обеспечивает минимальное время пересылки данных (не более одного цикла) и возможность параллельной обработки, сравнимой по эффективности с показателями непрограммируемой логической схемы. Заявленная скорость передачи данных по "вертикальному" и "горизонтальному" каналу составляет 816 Гбит/с при тактовой частоте 200 МГц.

Площадь ядра прототипа процессора, представленного на конференции - 3,1 кв.мм, выделяемая мощность - 0,25 Вт. По сведениям разработчиков, он в 70 превосходит по производительности и в 13 - по энергетической эффективности традиционные DSP.

Источник: Renesas Technology