Компании Hitachi и Renesas сообщают о разработке новой технологии соединения полупроводниковых чипов, позволяющей, во-первых, обойтись без использования внутренних проводников, а во-вторых, создавать микросхемы, чья толщина более чем вполовину (на 60%) меньше, чем у современных SiP (system in package).

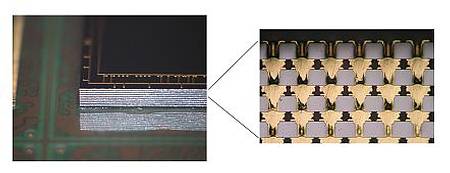

Заметим, правда, что внутренние проводники в SiP Hitachi и Renesas все же имеются – просто для соединения двух кристаллов не требуется пайки или дополнительных технологических процессов: золоченые электроды соединяются друг с другом примерно так же, как разные кубики конструктора “LEGO” (см. рисунок).

Толщина самих чипов составляет 30-50 мкм, а толщина готовой двухслойной микросхемы – не более 0,5 мм. По данным Hitachi и Renesas, самая тонкая SiP-микросхема конкурентов обладает толщиной около 1,25 мм.