Согласно сообщению Intel, специалистам компании удалось совершить существенный прорыв в использовании новых материалов для производства чипов. Согласно этому заявлению, использование новых материалов позволит значительно сократить утечки тока, а значит значительным образом снизить энергопотребление микросхем и их тепловыделение.

Итак, уже в 2007 году Intel намерена начать использование специальных high-k диэлектриков в затворах транзисторных переходов, что, по мнению специалистов, позволит снизить утечки тока как минимум в 100 раз! Согласно известному Закону Мура, количество транзисторов в процессорах к тому времени вполне может приблизиться к 1 млрд. Планируется, что в 2007 году компания перейдет к нормам 45 нм техпроцесса. Именно на данном этапе привычный диоксид кремния в затворах будет заменен на пока что неназванный high-k диэлектрик. Наряду с этим, компания также планирует отойти от использования добавок поликристаллического кремния при формировании электрода затвора транзистора, и начать использование двух различных металлов, соответственно, для создания переходов в NMOS или PMOS типах транзисторов.

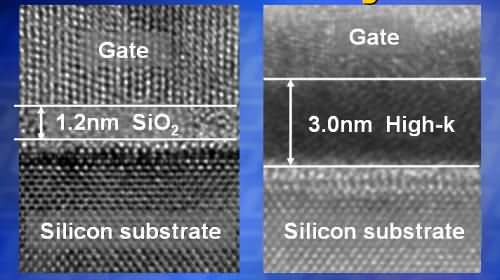

Суть нынешней проблемы с утечками, если обрисовать это схематически, заключается в следующем: толщина слоя диоксида кремния, применяемого нынче в затворах транзисторов в качестве диэлектрика, доведена до 5 атомов, что в свою очередь, приводит к туннелированию электронов сквозь слой окисла во "включенном" состоянии и увеличению энергопотребления. Переход к использованию high-k материалов ведет к тому, что ток, текущий по переходу во включенном состоянии, лишь незначительно превышает этот показатель в закрытом состоянии, и, соответственно, можно говорить о значительном снижении утечек.

Сам эффект снижения утечек от применения high-k окислов, как таковой, известен уже давно, однако, до сих пор ученые находятся в поиске материалов, наиболее подходящих для таких целей. Применение уже известных high-k материалов, например, оксида гафния, циркония и других обычно приводит к существенному снижению тока в канале под диэлектриком затвора, плюс, приводит к серьезным проблемам при установке порогового напряжения срабатывания затвора, особенно в транзисторах PMOS-типа.

Ожидается, что подробности о технологии применения новых high-k диэлектриках будут представлены Робертом Чоу (Robert Chau), ведущим разработчиком лаборатории Intel в Хиллсборо, Орегон, в четверг, на конференции International Gate Insulator Workshop в Токио. Презентация подробно описывает создание транзисторов NMOS и PMOS типов с физической длиной затвора порядка 80 нм и применением диэлектриков толщиной порядка 1,4 нм (14 Ангстрем).