Несмотря на то, что на проходившем мероприятии AMD Technology Analyst Day СТО (Chief Technology Officer) компании AMD Фил Гестер (Phil Hester) упорно не называл название предстоящей архитектуры, но было ясно, что речь идет именно о K8L, о которой мы уже довольно подробно рассказывали в наших новостях, но за вчерашний день вся эта информация всплыла заново и не один раз на многих информационных лентах.

О новой схеме работы кэш-памяти мы уже подробно рассказывали ранее и в сегодняшней новости. Приведем еще пару слайдов с презентации новой технологии AMD, поясняющие структуру ядра K8L-процессоров:

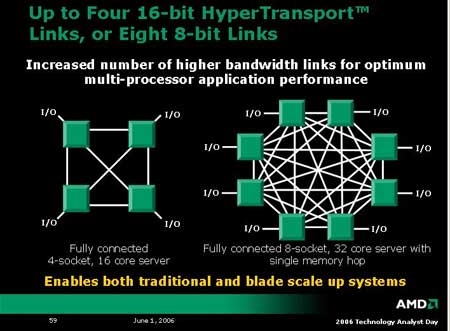

Четыре 16-бит и восемь 8-бит линии связи шины HyperTransport 3

Четыре 16-бит и восемь 8-бит линии связи шины HyperTransport 3

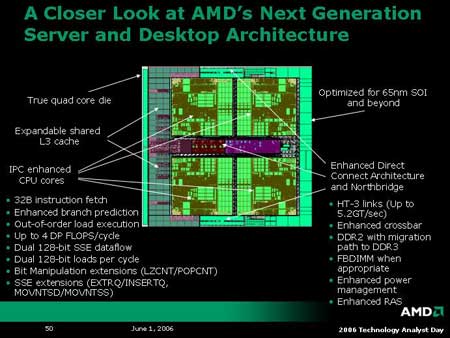

Особенности ядра AMD K8L

Особенности ядра AMD K8L

Одним из важных нововведений (особенностей) новой архитектуры будет DICE (Dynamic Independent Core Engagement), - технология, позволяющая каждому процессорному ядру иметь в каждый момент времени своё энергосостояние (power-state, p-state). Это позволит процессору архитектуры K8L динамически изменять потребление энергии, автоматически заботясь о ее сбережении. В свою очередь процессоры Intel Core имеют c-states, но как было показано на презентации AMD, процессоры ее новой архитектуры могут останавливать работу конкретного ядра полностью. Насколько данное "преимущество" технологии окажется эффективнее - покажет практика сравнения готовых продуктов в недалеком будущем.

Новая шина позволит создавать более эффективные машины-серверы с использованием процессоров Opteron на новой архитектуре. Текущие конфигурации имеют 4 или 8 процессорных сокетов и не более. Связано это с тем, что каждый процессор имеет только 3 линии связи по шине HyperTransport. Как и сообщалось ранее, а теперь подтверждено г-ном Гестером, новые Opteron будут иметь 4 линии связи по 16-бит HyperTransport-3, частота которой возрастет до 2,6 ГГц. С такой широкой пропускной способностью, которую обеспечивает HyperTransport-3, эффективность многопроцессорных (например, 8-процессорных) серверов значительно возрастет, т.к. все 32 ядра будут иметь полноскоростное подключение по шине. Каждый процессор при такой схеме получает быстрый доступ к любому из восьми имеющихся банков памяти.